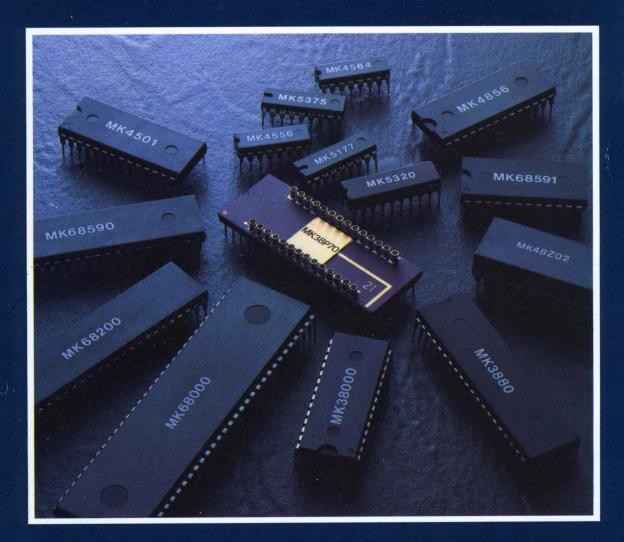

# MOSTEK 1984/1985

MICROELECTRONIC DATA BOOK

.

·

# 1984/1985 MICROELECTRONIC DATA BOOK

Copyright © 1984 Mostek Corporation (All rights reserved)

Trade Marks Registered ®

Mostek reserves the right to make changes in specifications at any time and without notice. The information furnished by Mostek in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Mostek for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Mostek.

The "PRELIMINARY" designation on a Mostek data sheet indicates that the product is not characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without notice.

The "TARGET SPECIFICATION" designation on a Mostek data sheet indicates that the product is not yet available. The TARGET SPECIFICATION is an initial disclosure of specification goals for the product. The specifications are subject to change, are based on design goals, and are not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in specifications at any time and without notice.

The "PRODUCT PROFILE" designation on a Mostek literature item indicates that the product is not available as of the print date of this document and that the specification goals have not yet been fully established. the PRODUCT PROFILE is an initial disclosure of a new product's features and general information. The information given in the PRODUCT PROFILE is subject to change and is not guaranteed. Mostek Corporation or an authorized sales representative should be consulted for current information before using this product. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek. Mostek reserves the right to make changes in the product at any time and without notice.

The "APPLICATION BRIEF" or "APPLICATION NOTE" designation on a Mostek literature item indicates that the literature item contains information regarding Mostek product features and/or their varied applications. The information given in the APPLICATION BRIEF or APPLICATION NOTE is believed to be accurate and reliable; however, the information is subject to change and is not guaranteed. No responsibility is assumed by Mostek for its use; nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Mostek.

PRINTED IN USA July 1984 Publication No. 4420479

# 1984/1985 MICROELECTRONIC DATA BOOK

# 1984/1985 MICROELECTRONIC DATA BOOK

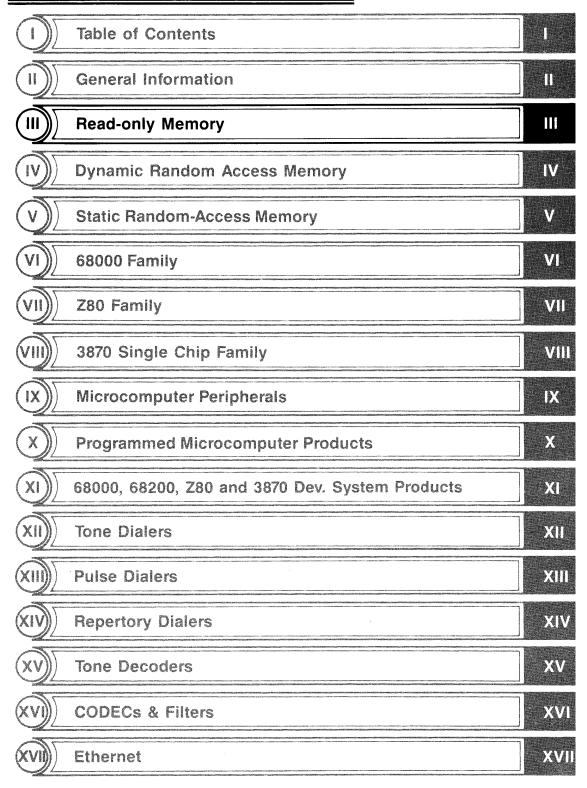

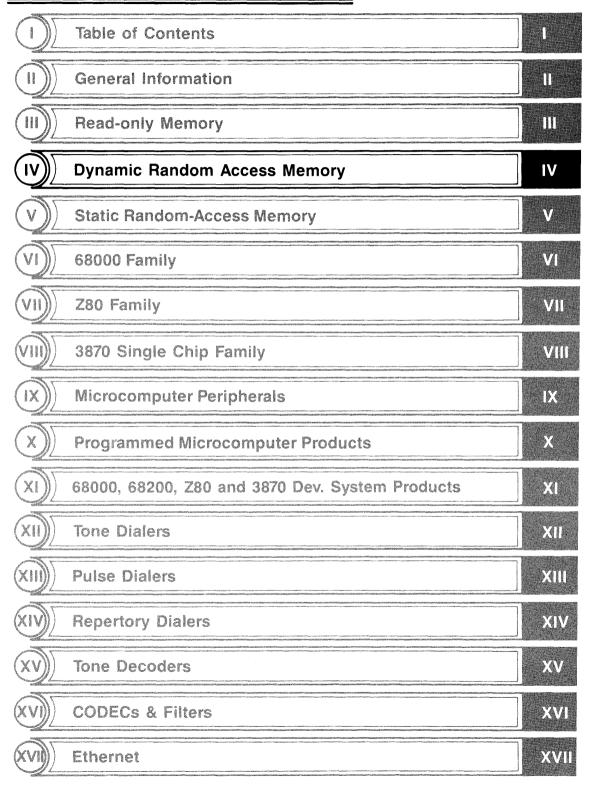

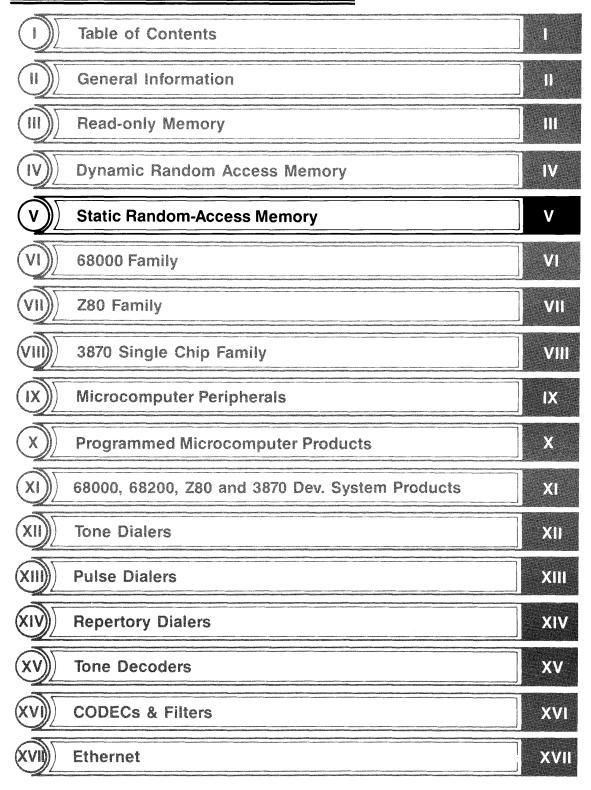

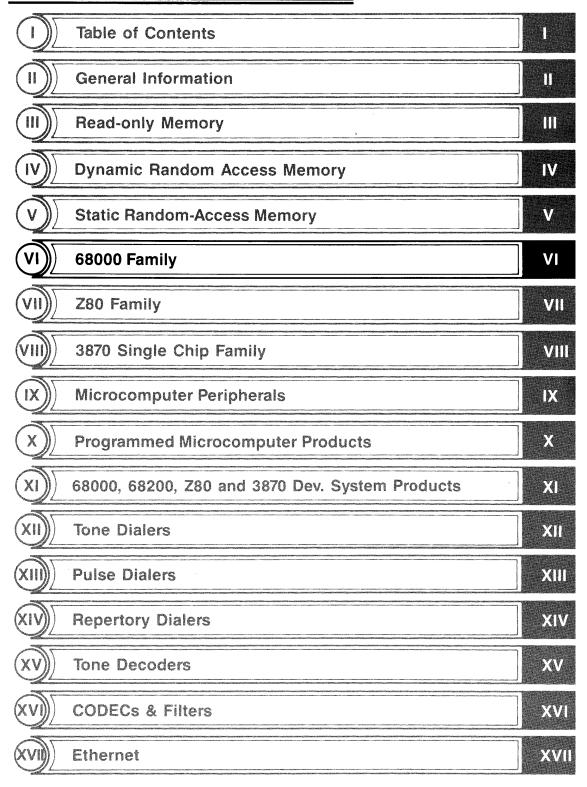

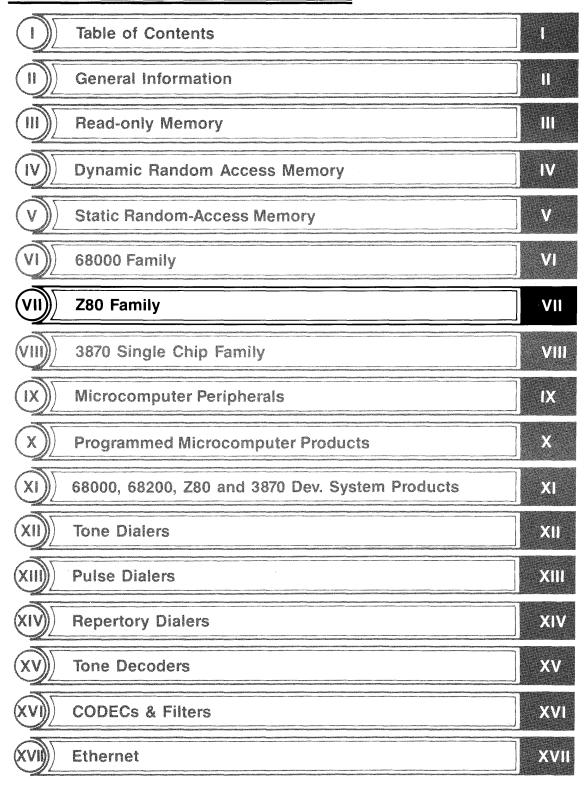

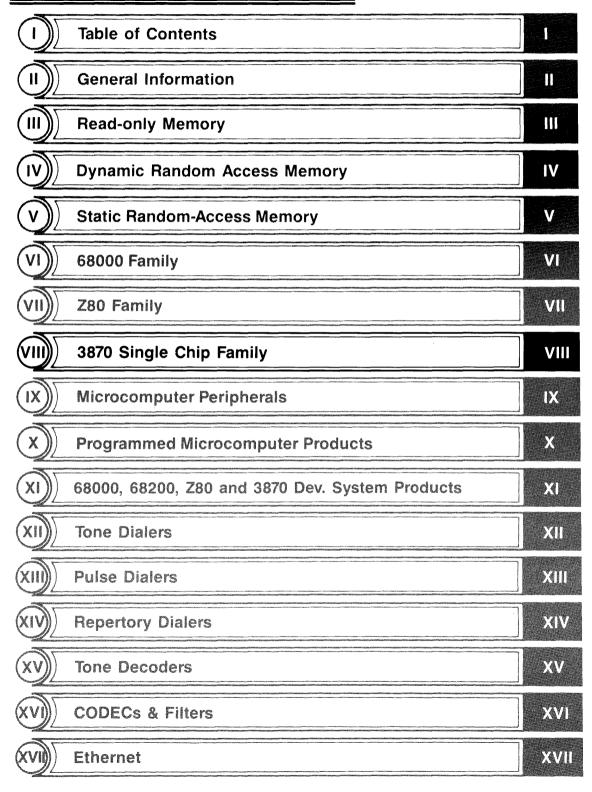

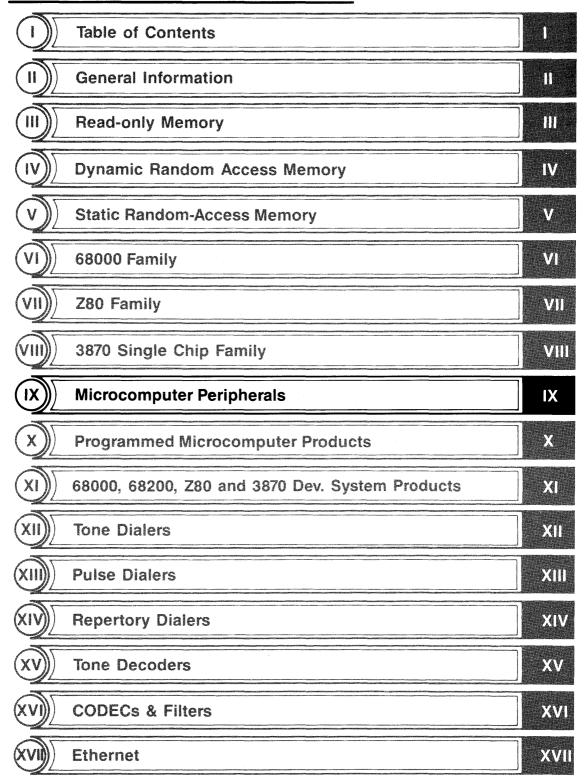

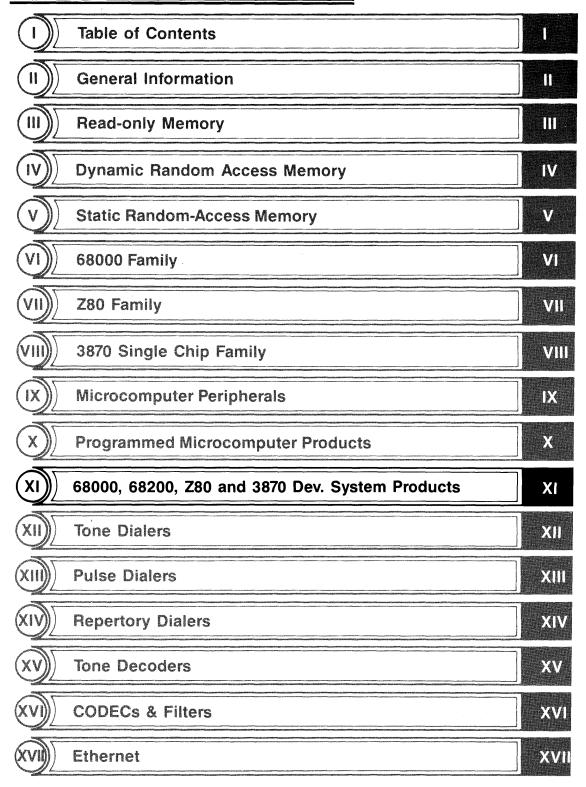

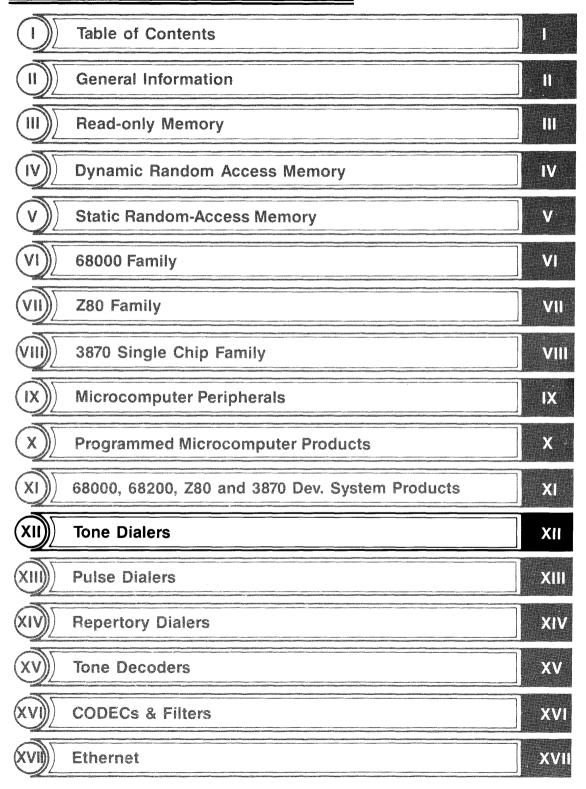

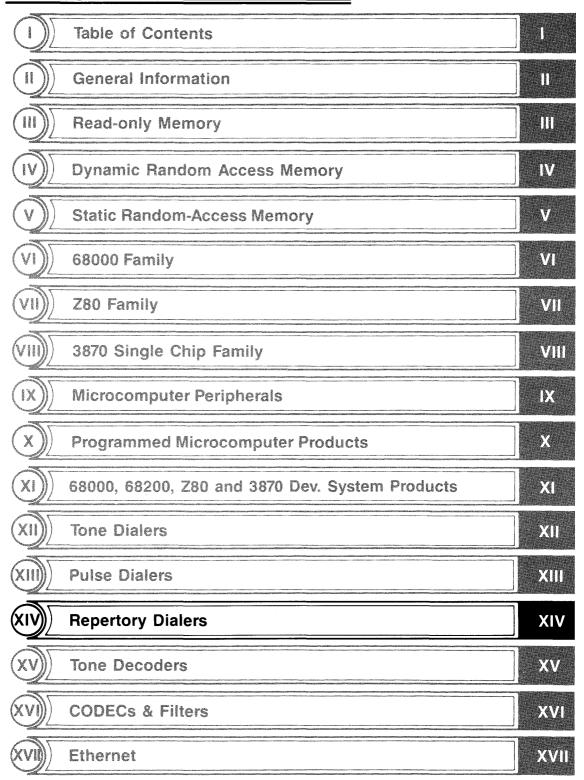

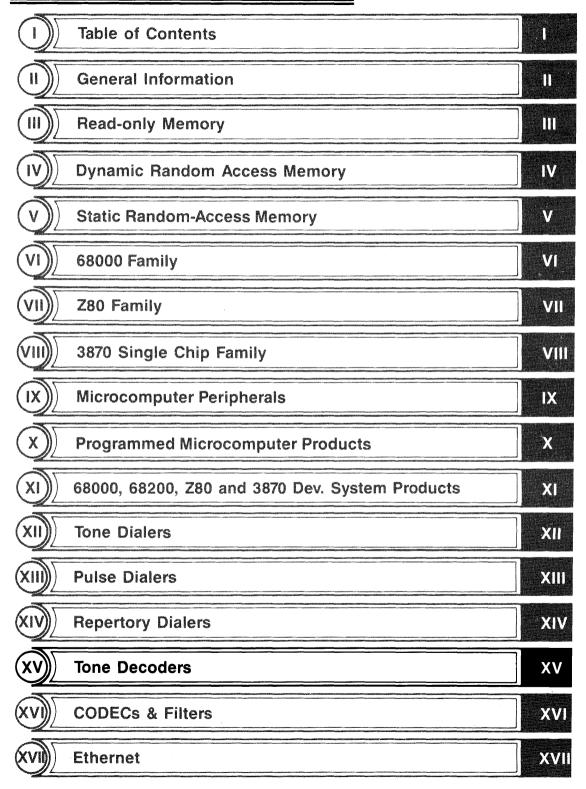

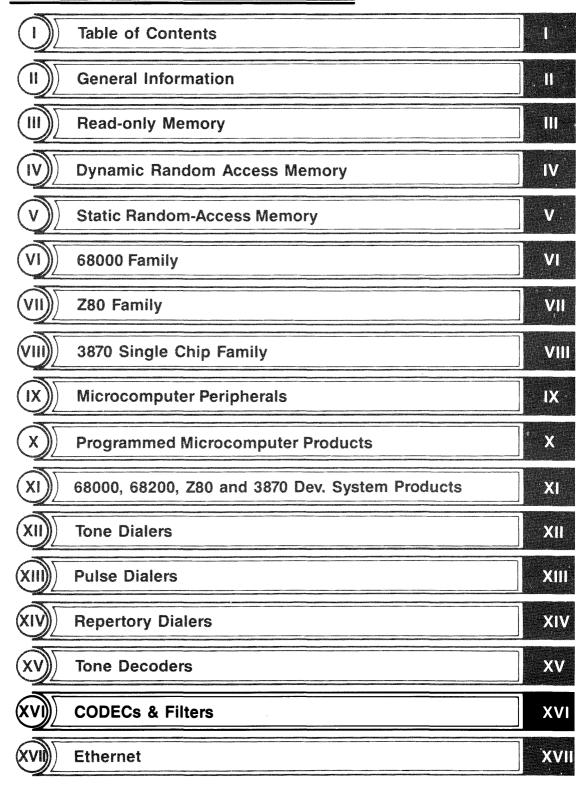

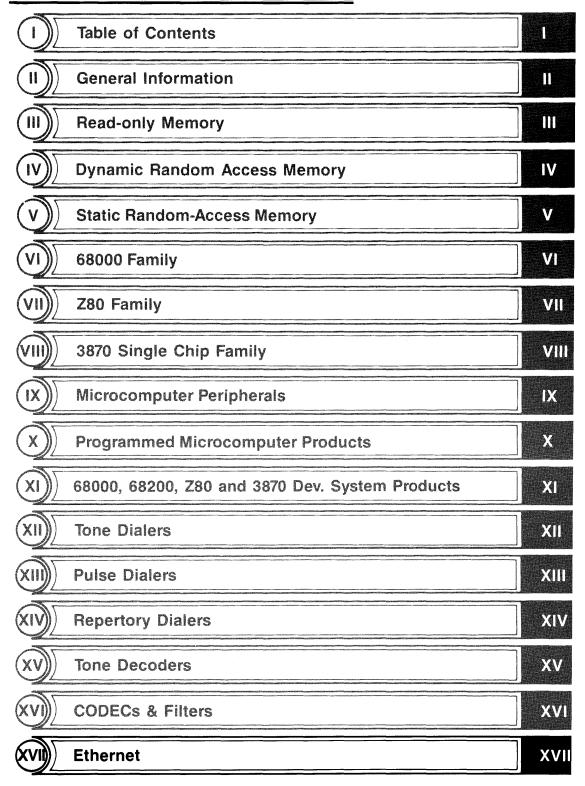

# TABLE OF CONTENTS

| · 1.  | Table of Contents                                           |

|-------|-------------------------------------------------------------|

|       | Functional Index                                            |

|       |                                                             |

| II.   | General Information                                         |

|       | Mostek Profile                                              |

|       | Package DescriptionsII-5<br>Order InformationII-14          |

|       | U.S. and Canadian Sales Offices                             |

|       | U.S. and Canadian Representatives                           |

|       | U.S. and Canadian Distributors                              |

|       | International Sales Reps/Distributors II-19                 |

|       | International Marketing OfficesII-19                        |

|       | European Sales Reps/Dist                                    |

| MEMOF | Y COMPONENTS                                                |

|       | Read-only Memory                                            |

|       | MK36000 (P/J/N) Series                                      |

|       | MK37000 (P/J/N) Series                                      |

|       | MK38000 (P/N)-25 III-9                                      |

|       | Guidelines for Submitting & Verifying Customer ROM Patterns |

|       | MK3901M(P/N) Series III-17                                  |

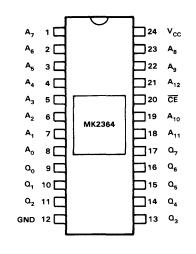

|       | MK2364 (P/N)-20/25 III-19                                   |

|       | MK2365 (P/N)-20/25                                          |

|       | MK23128 (P/N)-20/25 III-27                                  |

| IV.   | Dynamic Random Access Memory                                |

|       | MK4027 (J/N)-2/3 IV-1                                       |

|       | MK4027 (J/N)-4                                              |

|       | MK4116 (J/N/E)-2/3                                          |

|       | MK4516 (N/J)-9                                              |

|       | MK4516 (N/J)-20                                             |

|       | MK4564 (P/N/J/E)-12                                         |

|       | MK4564 (P/N/J/E)-15/20 IV-71                                |

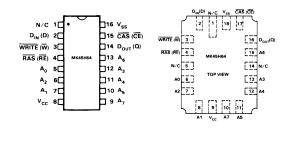

|       | MK45H64 (P/N/J/E)-8/10/12                                   |

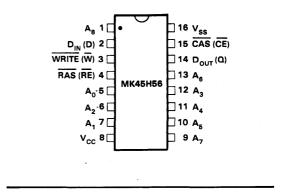

|       | MK45H56 (P/N/E)-8/10/12                                     |

|       | MK4856 (N/P/J/E)-10/12/15 IV-93                             |

# V. Static Random-Access Memory

| VK4104 (P/J/N) Series                            |

|--------------------------------------------------|

| MK4801A (P/J/N)-1/2/3/4                          |

| MK4801A (P/J/N)-55/70/90                         |

| NK4701 (N)-20                                    |

| MK6116 (J/N)-15/20/25/MK6116L (J/N)-15/20/25V-21 |

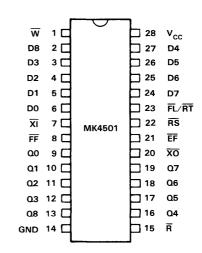

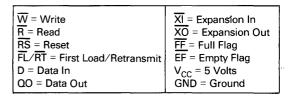

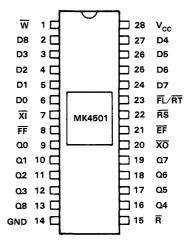

| MK4501 (N)-8/10                                  |

| WK4501 (N)-12/15/20                              |

| MK4511(N/E)-15........                           |

| MK48C02/MK48C02L (N)-15/20/25V-43                |

| MK48Z02 (B)-15/20/25                             |

### **MICROCOMPUTER COMPONENTS**

### VI. 68000 Family

|      | MK68000                                            | CPU                      | Central Processing Unit                                                                                                                                                                 |

|------|----------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

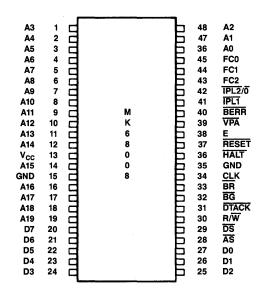

|      | MK68008                                            | CPU                      | Central Processing Unit                                                                                                                                                                 |

|      | MK68010                                            | VMM                      | Virtual Memory Microprocessor                                                                                                                                                           |

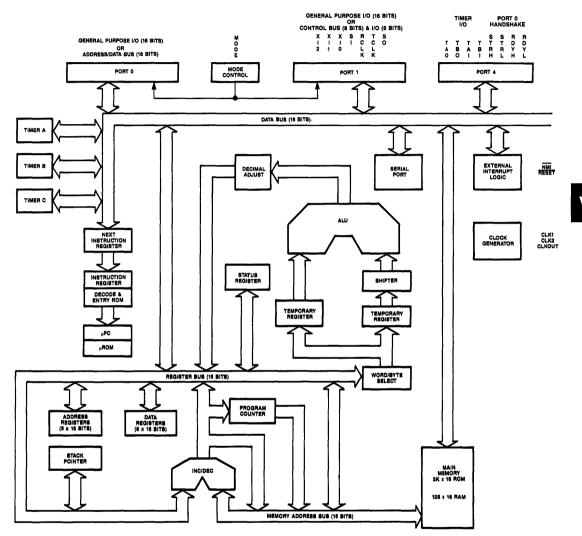

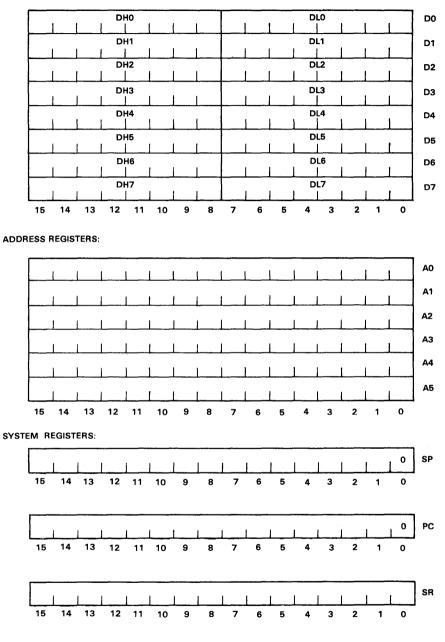

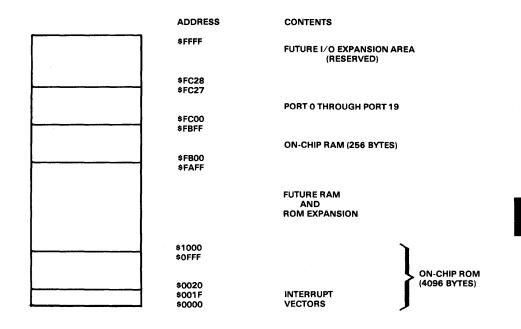

|      | MK68200                                            | MCU                      | 16-Bit Microcomputing UnitVI-65                                                                                                                                                         |

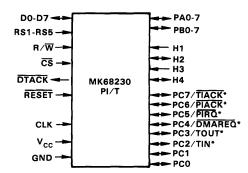

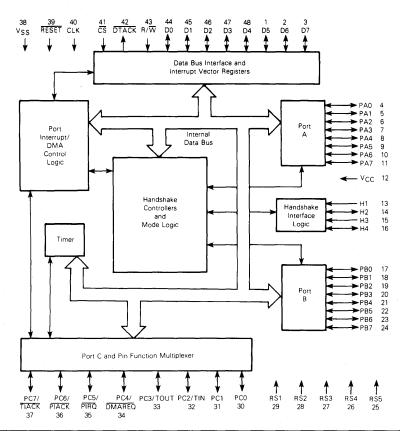

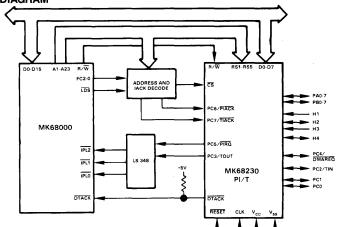

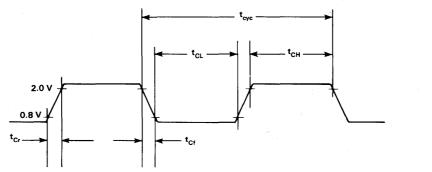

|      | MK68230                                            | PI/T                     | Parallel Interface/TimerVI-111                                                                                                                                                          |

|      | MK68451                                            | MMU Adv. Inf.            | Memory Management UnitVI-121                                                                                                                                                            |

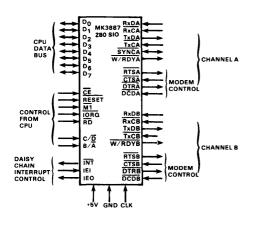

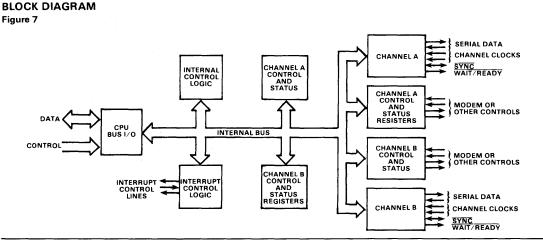

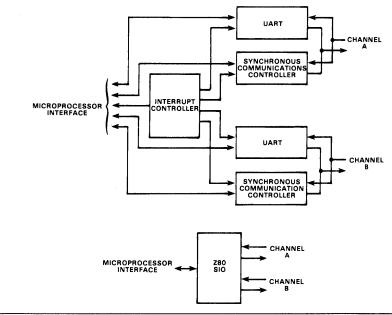

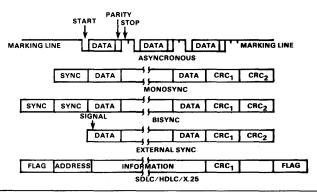

|      | MK68564                                            | SIO                      | Serial Input/Output ControllerVI-125                                                                                                                                                    |

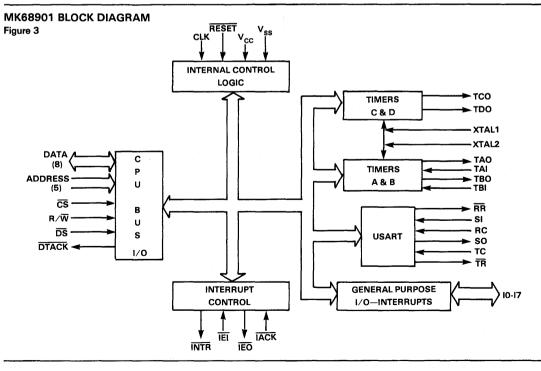

|      | MK68901                                            | MFP                      | Multi-Function PeripheralVI-137                                                                                                                                                         |

|      |                                                    |                          |                                                                                                                                                                                         |

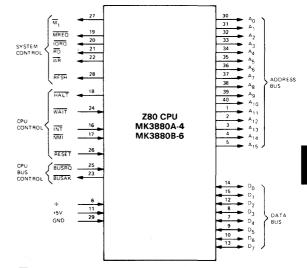

| VII. | Z80 Family                                         |                          |                                                                                                                                                                                         |

| VII. | <b>Z80 Family</b><br>MK3880                        | A&B CPU                  | Central Processing UnitVII-1                                                                                                                                                            |

| VII. |                                                    | A&B CPU<br>PI0           | Central Processing Unit                                                                                                                                                                 |

| VII. | MK3880                                             |                          |                                                                                                                                                                                         |

| VII. | MK3880<br>MK3881                                   | PIO                      | Parallel I/0 ControllerVII-9                                                                                                                                                            |

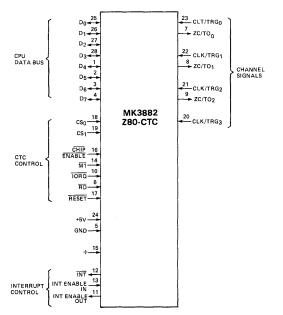

| VII. | MK3880<br>MK3881<br>MK3882                         | PI0<br>CTC               | Parallel I/0 Controller                                                                                                                                                                 |

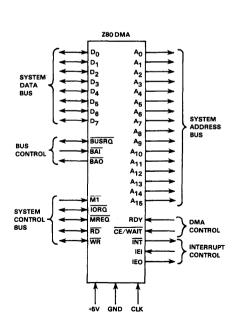

| VII. | MK3880<br>MK3881<br>MK3882<br>MK3883               | PIO<br>CTC<br>DMA        | Parallel I/0 Controller         VII-9           Counter Timer Circuit         VII-17           Direct Memory Access Controller         VII-25                                           |

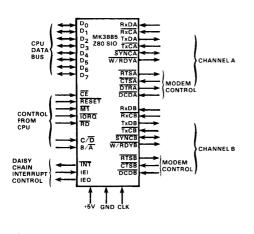

| VII. | MK3880<br>MK3881<br>MK3882<br>MK3883<br>MK3884/5/7 | PIO<br>CTC<br>DMA<br>SIO | Parallel I/0 Controller       VII-9         Counter Timer Circuit       VII-17         Direct Memory Access Controller       VII-25         Serial Input/Output Controller       VII-43 |

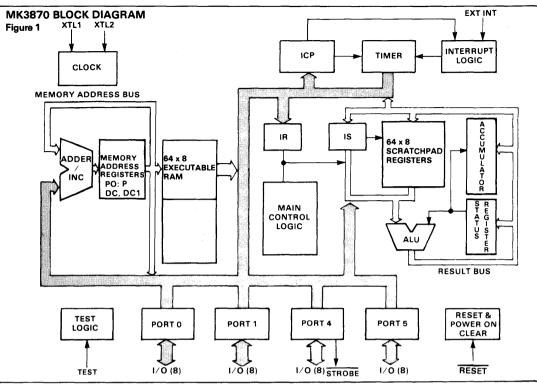

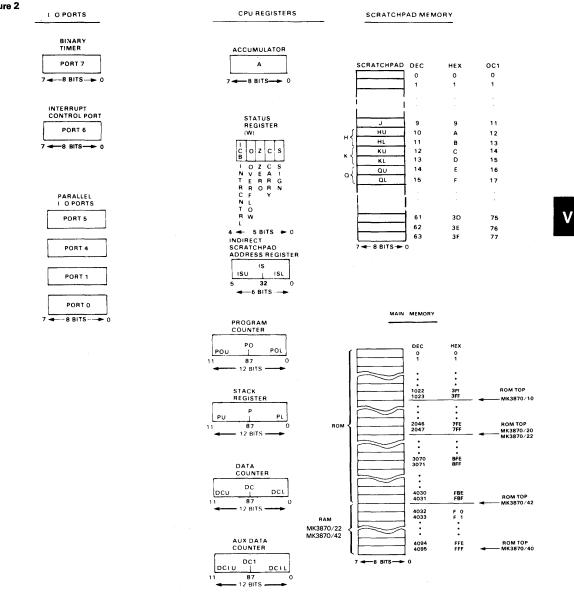

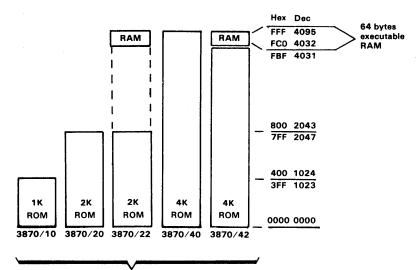

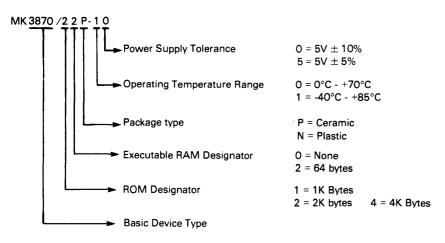

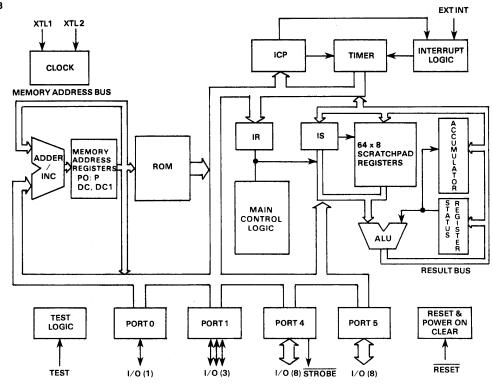

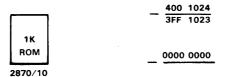

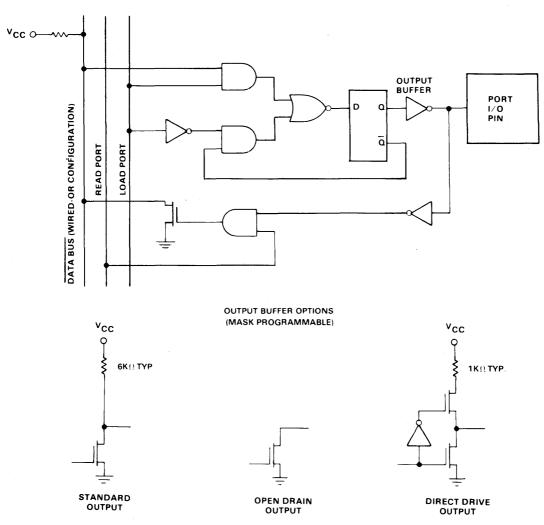

### VIII. 3870 Single Chip Family

| 3870 Family Selection Guide | · · · · · · · · · · · · · · · · · · · | -1   |

|-----------------------------|---------------------------------------|------|

| MK3870/38P70                | Single Chip MicrocomputerVI           |      |

| MK2870                      | 28 Pin MicrocomputerVIII              | 1-31 |

| MK3873/38P73                | Serial Port MicrocomputerVIII         | 1-49 |

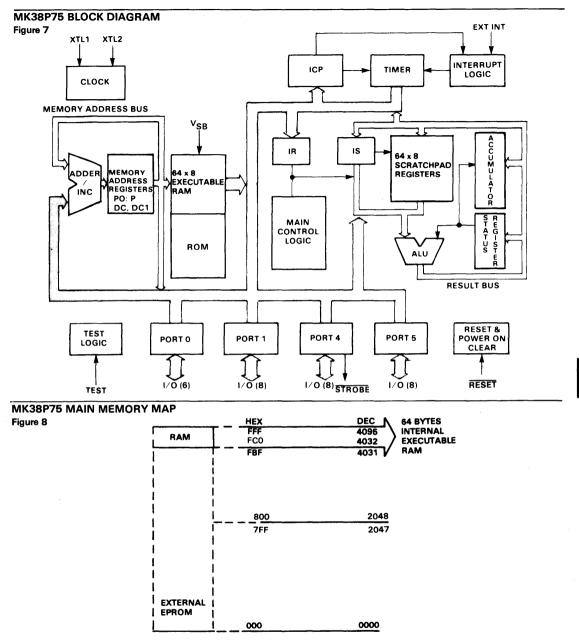

| MK3875/38P75                | Stand By RAM MicrocomputerVII         | 1-75 |

### **IX. Microcomputer Peripherals**

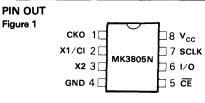

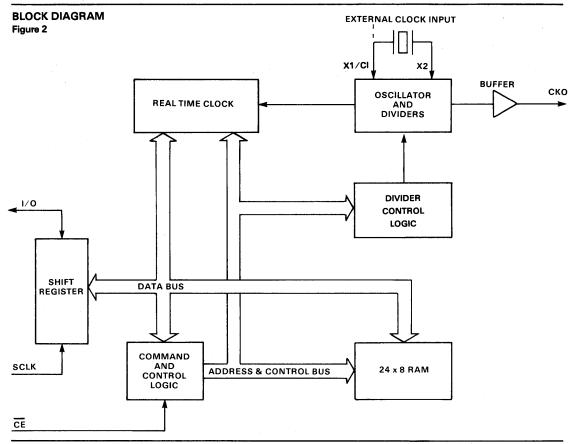

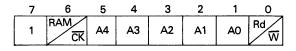

| MK3805N | CMOS Microcomputer Clock/RAMIX-1             |

|---------|----------------------------------------------|

| MK3807  | Programmable CRT Video Control Unit VCUIX-13 |

|         |                                              |

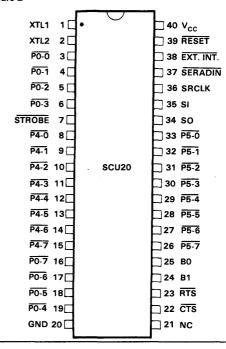

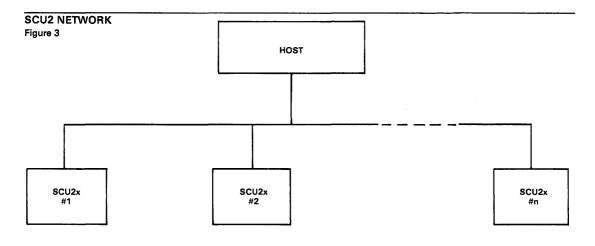

### X. Programmed Microcomputer Products SCU20 Serial Control

| Serial Control | Unit | X-1 |

|----------------|------|-----|

|----------------|------|-----|

### XI. 68000, 68200, Z80 and 3870 Development System Products

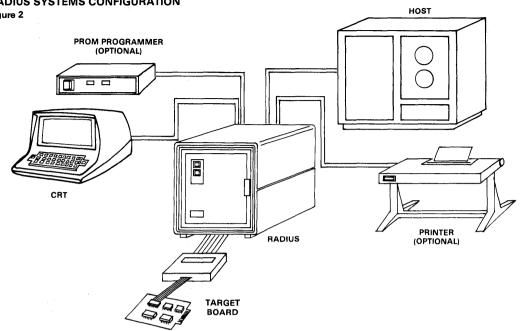

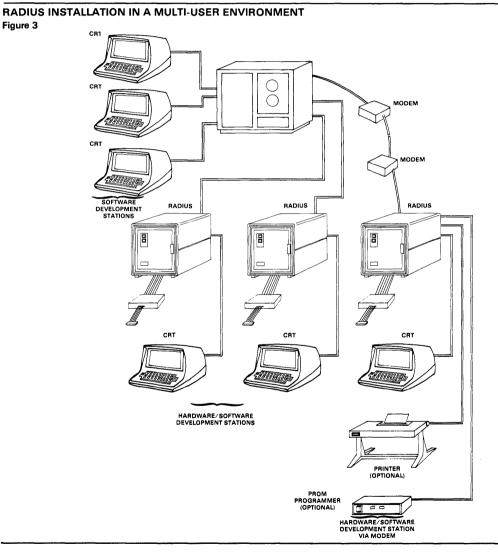

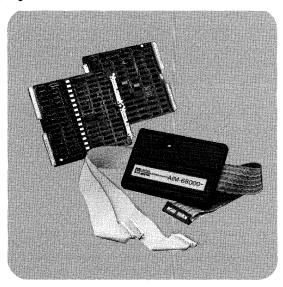

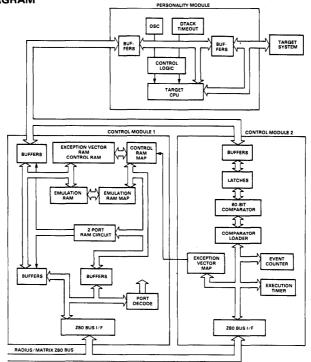

| Radius              | Remote Development StationXI-1                                  |

|---------------------|-----------------------------------------------------------------|

| AIM68000            | Application Interface ModuleXI-5                                |

| AIM68200            | Application Interface ModuleXI-11                               |

| AIMZ80BE            | Application Interface Module for Z80XI-15                       |

| AIM7XE              | Application Interface Module for 3870 SeriesXI-19               |

| EPP1                | EPROM ProgrammerXI-23                                           |

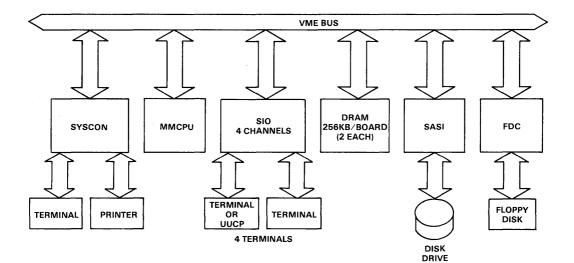

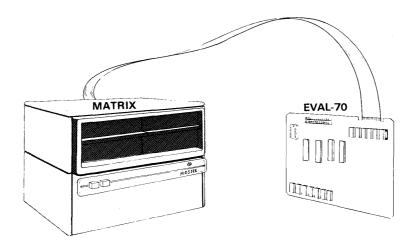

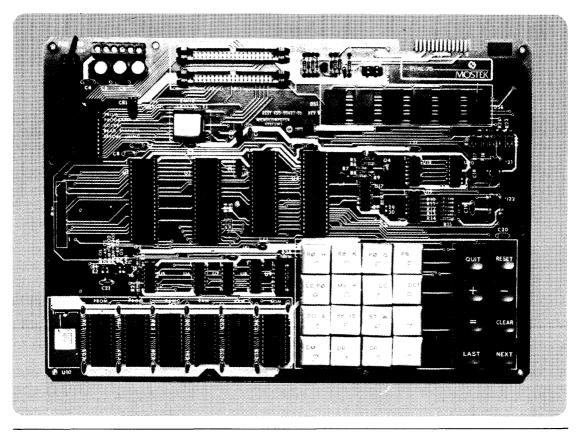

| Matrix 68K          | Microcomputer SystemXI-29                                       |

| Matrix 80/SDS       | Microcomputer Development SystemXI-31                           |

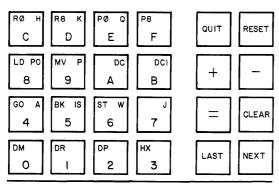

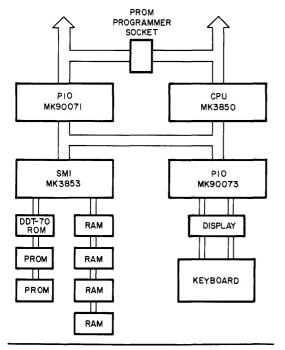

| Eval 70             | Evaluation System for 3870 XI-35                                |

| M/OS-80             | Flexible Disk Operating SystemXI-39                             |

| MICROSOFT           | M80/L80, Basic-80, Bascom, Fortran-80XI-43                      |

| ASM-68000/LNK-68000 | Structured Macro Cross Assembler/Relocating Linkage EditorXI-45 |

| ASM-68200/LNK-68200 | Structured Macro Cross Assembler/Relocating Linkage EditorXI-49 |

| CRASM-70            | Cross-Assembler for 3870XI-53                                   |

| Ordering Guide      | Development Systems ProductsXI-55                               |

### **TELECOMMUNICATIONS**

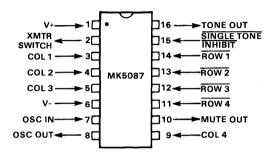

# XII. Integrated Tone Dialers

| MK5087 (N/P/J)                                            | . XII-1 |

|-----------------------------------------------------------|---------|

| MK5089 (N/P/J)                                            | . XII-7 |

| MK5087/89 Electronic Drive App. Brief                     | XII-13  |

| MK5380 (N/P/J)                                            | XII-15  |

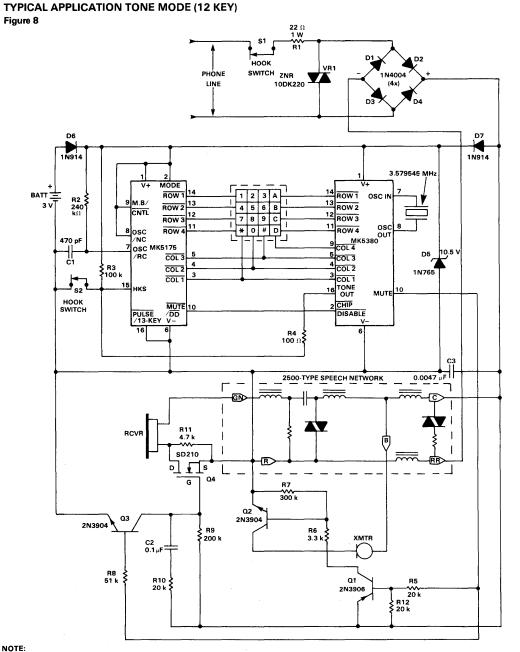

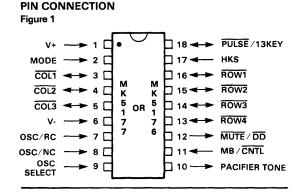

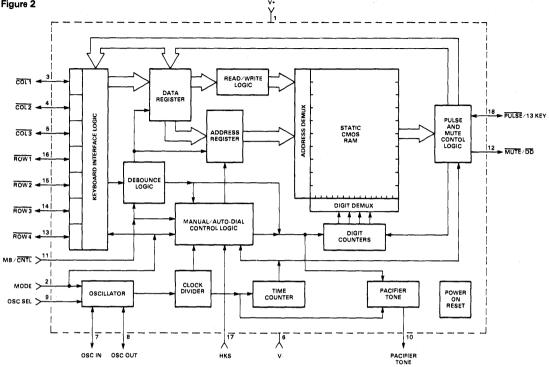

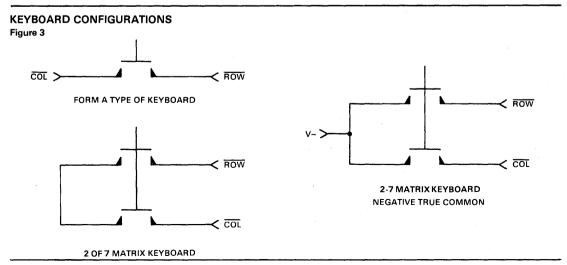

| MK5175/MK5380 Pulse/Tone Switchable Application App. Note | XII-23  |

| Tone II vs Tone III App. Brief                            | XII-27  |

| Loop Simulator App. Brief                                 |         |

|                                                           |         |

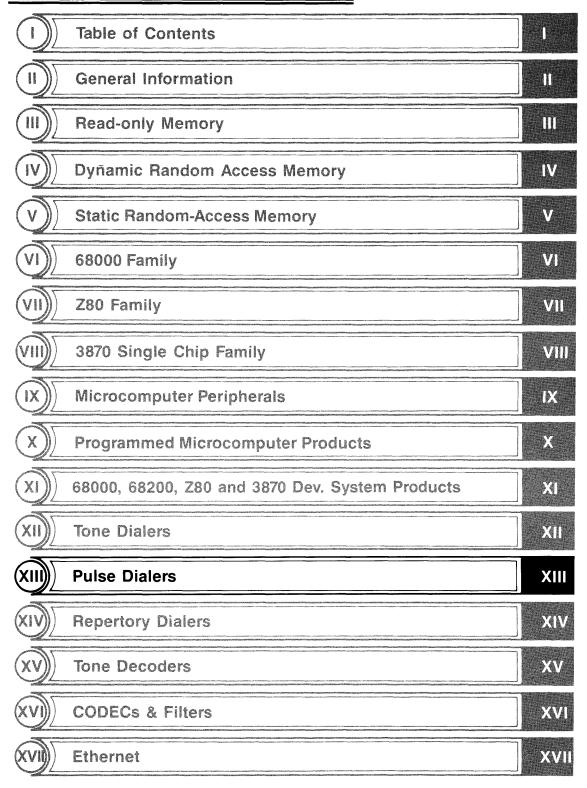

# XIII. Integrated Pulse Dialers with Redial

| MK50981 (N)-05                     | XIII-1  |

|------------------------------------|---------|

| MK50982 (N)                        | XIII-5  |

| MK50991 (N)                        | XIII-11 |

| MK50992 (N)-05                     | XIII-17 |

| Pulse Dialer Comparison App. Brief | XIII-21 |

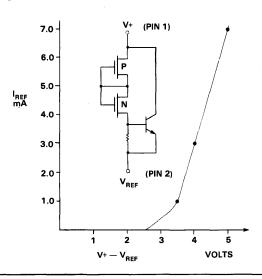

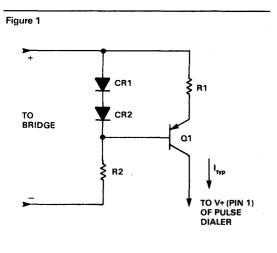

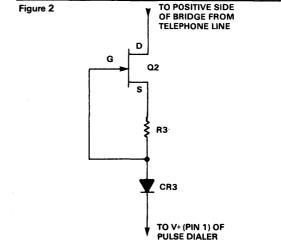

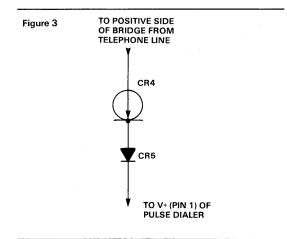

| Current Sources App. Brief         | XIII-23 |

# **XIV. Repertory Dialers**

| MK5175 (N)                                                | XIV-1   |

|-----------------------------------------------------------|---------|

| MK5175/MK5380 Pulse/Tone Switchable Application App. Note | XII-23  |

| MK5177 (N), MK5176 (N)                                    |         |

| MK5375                                                    |         |

| MK5374/MK5376                                             | XIV-33  |

| MK5370/MK5371/MK5372                                      | ′XIV-35 |

# XV. Integrated Tone Decoders

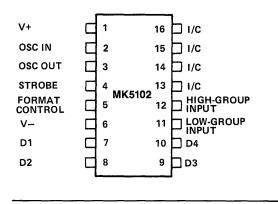

| MK5102 (N/P/J)XV                        | 1 |

|-----------------------------------------|---|

| MK5103 (N/P/J)XV-                       | 5 |

| MK5102/S3525A App. Brief                | 1 |

| DTMF Receiver System App. BriefXV-1     |   |

| MK5102 (N)-5 DTMF Decoder App. NoteXV-1 |   |

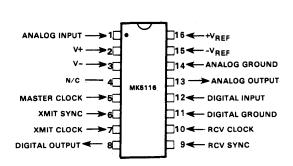

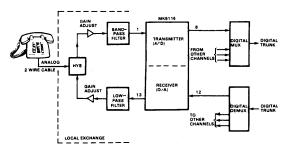

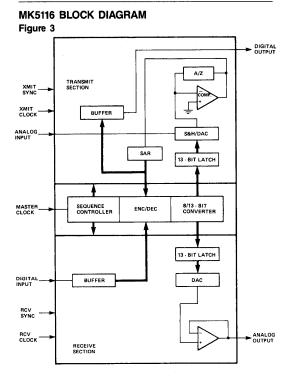

# XVI. CODECs & Filters

| MK5116    | (J/N)   | )  |   |   |    |    |     |    |    |    | •  |    |    |   |    |   |    |   | <br> |      |  | • |  |   |  |  |  |  |      |  |   |      | <br>  | X٧ | / -' | I |

|-----------|---------|----|---|---|----|----|-----|----|----|----|----|----|----|---|----|---|----|---|------|------|--|---|--|---|--|--|--|--|------|--|---|------|-------|----|------|---|

| MK5151    | (J/P)   | )  |   |   |    |    |     |    |    |    |    |    |    |   |    |   |    |   |      | <br> |  |   |  |   |  |  |  |  |      |  |   | <br> | . X   | VI | -1'  | I |

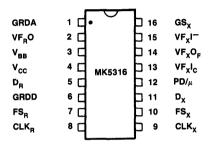

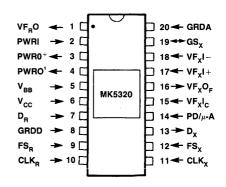

| MK5156    |         |    |   |   |    |    |     |    |    |    |    |    |    |   |    |   |    |   |      |      |  |   |  |   |  |  |  |  |      |  |   |      |       |    |      |   |

| MK5316    |         |    |   |   |    |    |     |    |    |    |    |    |    |   |    |   |    |   |      |      |  |   |  |   |  |  |  |  |      |  |   |      |       |    |      |   |

| MK5320    |         |    |   |   |    |    |     |    |    |    |    |    |    |   |    |   |    |   |      |      |  |   |  |   |  |  |  |  |      |  |   |      |       |    |      |   |

| MK5356    | i (J) . |    |   |   |    |    |     |    |    |    |    |    |    |   |    |   |    |   | <br> |      |  |   |  |   |  |  |  |  | <br> |  |   |      | <br>X | ٧ŀ | -37  | 7 |

| MK5326    |         |    |   |   |    |    |     |    |    |    |    |    |    |   |    |   |    |   |      |      |  |   |  |   |  |  |  |  |      |  |   |      |       |    |      |   |

| Integrate | ed PO   | СМ | С | O | DI | EC | ; ; | Te | cł | in | ol | οg | ју | ι | Jp | d | at | е | <br> |      |  |   |  | • |  |  |  |  | <br> |  | • |      | <br>X | ٧ŀ | -4'  | 1 |

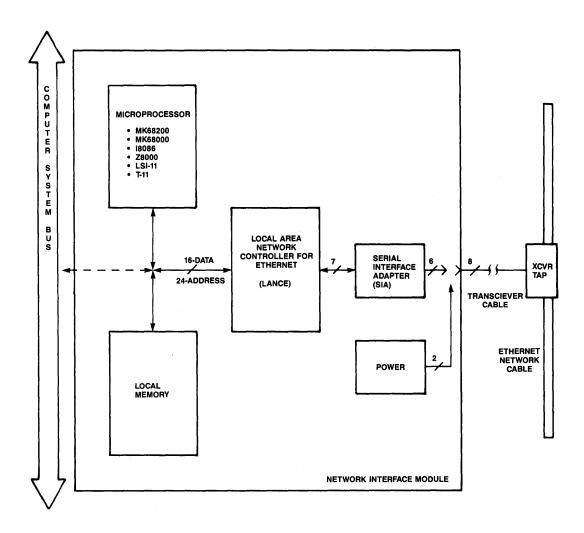

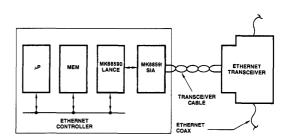

# XVII. Ethernet

| MK68590 | LANCE | Local Area Network Controller for EthernetXVI |

|---------|-------|-----------------------------------------------|

| MK68591 | SIA   | Serial Interface AdapterXVII-                 |

I-4

# 1984/1985 MICROELECTRONIC DATA BOOK

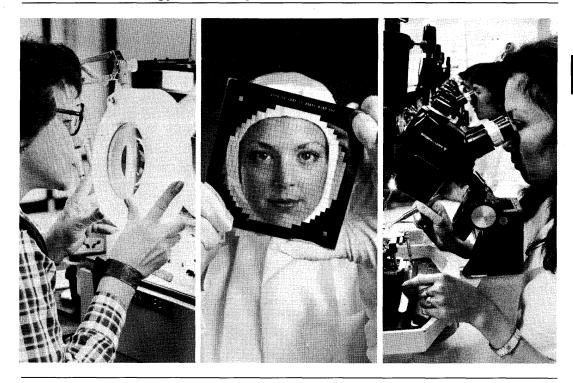

# Mostek - Technology For Today And Tomorrow

# Quality products based on efficient, innovative designs.

Today's sophisticated applications require electronic components and subsystems that deliver high performance, high reliability. Mostek dedicates vast resources to research and development to give you exactly what you need: efficient, cost-effective solutions to your specific design needs.

Quality and reliability are built into Mostek products every step of the way, from the initial design stages through manufacturing and testing. And we follow up with extensive product training, sales and customer support. All to achieve Mostek's final objective—outstanding performance in your system.

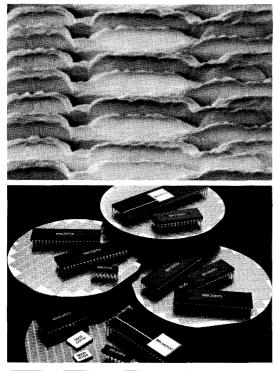

Mostek combines state-of-the-art NMOS and CMOS process technology with smart design to develop high-quality products that are also highly manufacturable. Because of the efficient design of our 64K DRAM, it was possible to increase production from six million units in 1982 to more than 41 million in 1983.

At Mostek, our goal is to provide faster, denser, lower power products—at competitive prices. Through aggressive research and development, innovative design and commitment to quality, Mostek is ready to anticipate and meet your needs now, and in the future.

### MEMORIES

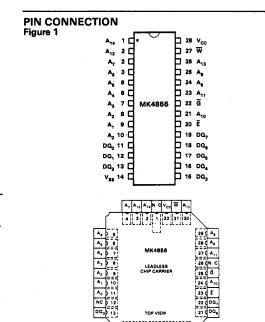

Mostek is an industry leader in the design and manufacture of dynamic RAMs, including the MK45H64, the world's fastest DRAM, and the MK4856, the first 32K×8 256K DRAM. To meet the precise manufacturing requirements of the 256K DRAM, Mostek has more direct-step-on-wafer (DSW) machines on-line than any other manufacturer in the world. And more experience with those machines as well. Other Mostek memory product innovations include the first true non-volatile RAM and the BiPORT<sup>™</sup> series of interconnect devices.

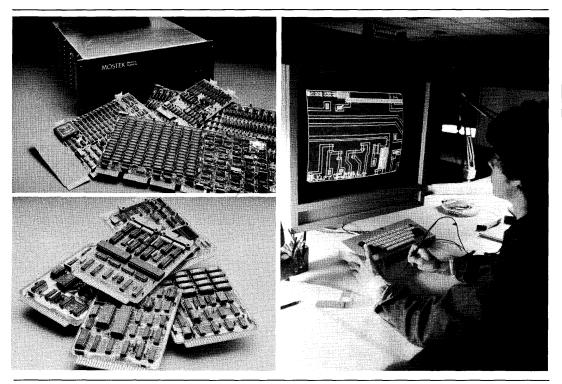

### MEMORY SYSTEMS

The performance and reliability of Mostek industry-standard circuits is built into all of our memory systems products. For example, the MK8200 general-purpose mass memory system delivers the fastest throughput and highest density currently available anywhere.

### SEMICUSTOM CIRCUITS

Mostek now offers the designer a way to reduce part count and increase system reliability and performance: a full family of 2- and 3-micron gate arrays. Mostek semicustom circuits let you design your circuits to your specific applications. And our captive photomask facility and largescale wafer production and assembly facilities make Mostek a turn-key vendor, unlike other semicustom suppliers.

### MILITARY

Mostek delivers the latest state-of-the-art microelectronics in military versions.

Many of our products are qualified to meet stringent military requirements, including the new MKB4501 BiPORT FIFO memory chip, screened to MIL-STD-883, Class B. And the MKB45H64, the world's fastest DRAM, is also now available to the armed forces through Mostek.

### **MICROCOMPONENTS**

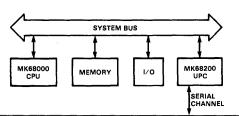

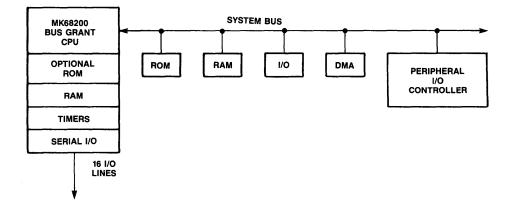

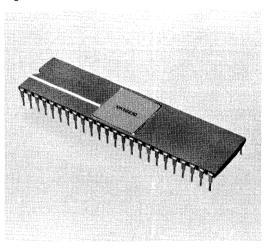

At Mostek, we're dedicated to improving the power and versatility of our MK68200 16-bit single-chip microcomputer and MK68000 microprocessor families. For example, our high-performance MK68200 microcomputer has the speed and power ideal for robotics and other complex tasks. And our MK68000 family of microprocessors and peripherals lets you quickly develop even the most sophisticated I/O-intensive applications.

### MICROCOMPONENT SUPPORT

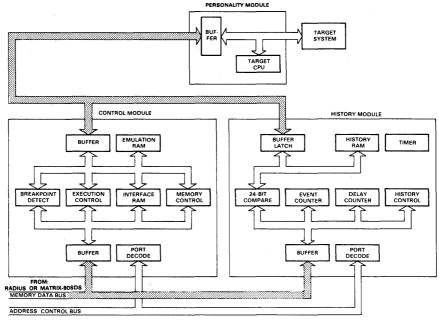

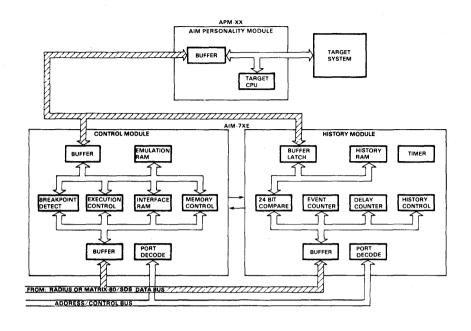

Mostek manufactures a complete line of emulation tools. With four different cards, Mostek supports its four different microprocessor families, including the new MK68200 microcomputer. By using any of our four Mostek AIM<sup>™</sup> modules with either the Mostek RADIUS<sup>™</sup> remote development station or the Mostek MATRIX<sup>™</sup> standalone development system, you get complete hardware/software development and debug capabilities at competitive prices.

### **MICROCOMPUTER SYSTEMS**

Mostek offers a full line of 8-bit STD-Z80 BUS microcomputer boards and systems. For 16-bit applications, Mostek VMEbus systems deliver high performance and expandability. And our new VME MATRIX 68K<sup>™</sup> is a multi-user, 16-bit development system featuring the UniPlus<sup>+™</sup> UNIX<sup>™</sup> System III operating system.

### COMMUNICATIONS

Mostek is the world's largest independent supplier of large-scale integrated circuits for telecommunications applications. Mostek participates in three major market segments—analog applications, digital applications (such as PBXs), and computer information networks. To meet the growing needs of the communications industry, our product line has been expanded recently to include single and repertory integrated dialer circuits capable of both tone and pulse dialing.

### SOFTWARE

Mostek provides powerful software development packages for 8- and 16-bit systems. For 8-bit microprocessors, Mostek offers the CP/M<sup>™</sup> V3.0 industrystandard operating system. To meet the needs of rapildly growing 16-bit applications, Mostek offers the versatile VME MATRIX 68K, a multi-user development system which employs the UniPlus<sup>™</sup> UNIX operating system. UniPlus<sup>±</sup> is derived from the UNIX System III.

# MICROELECTRONIC PRODUCTS

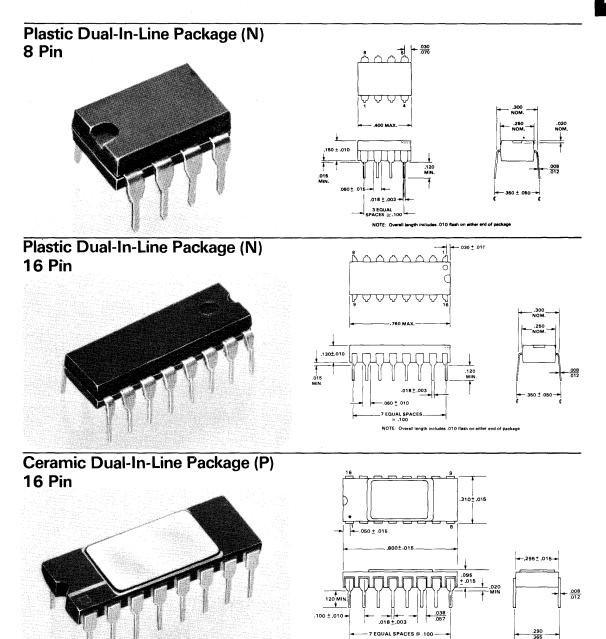

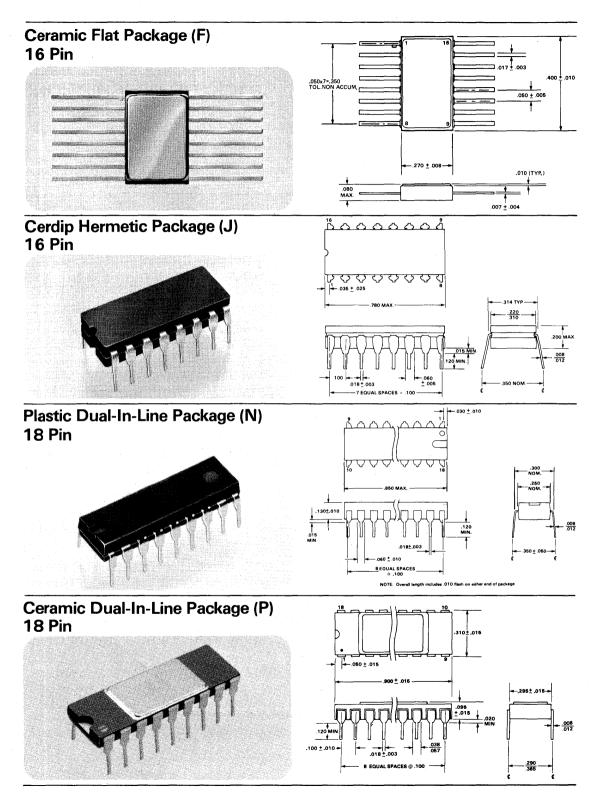

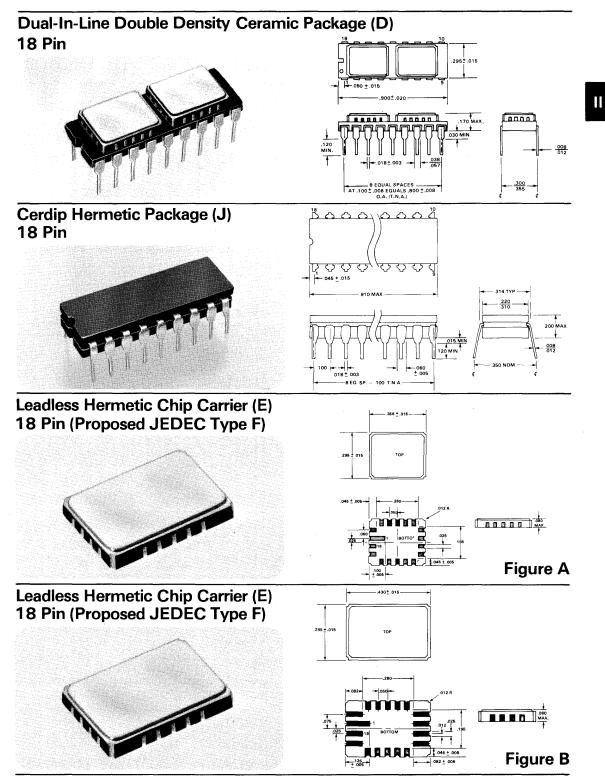

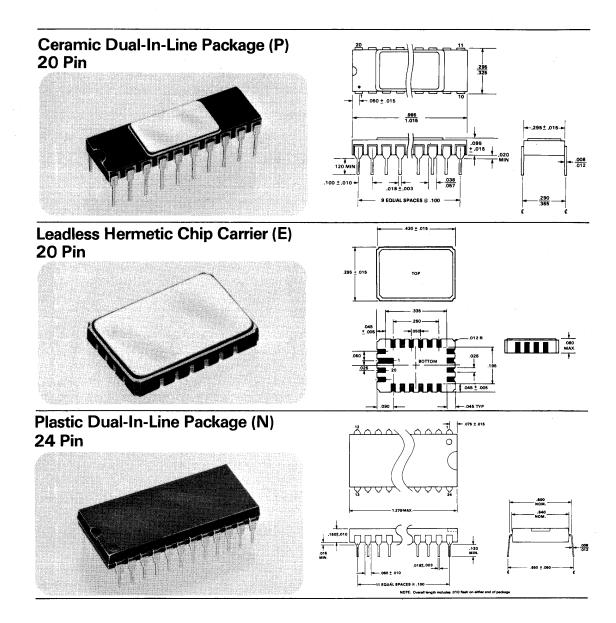

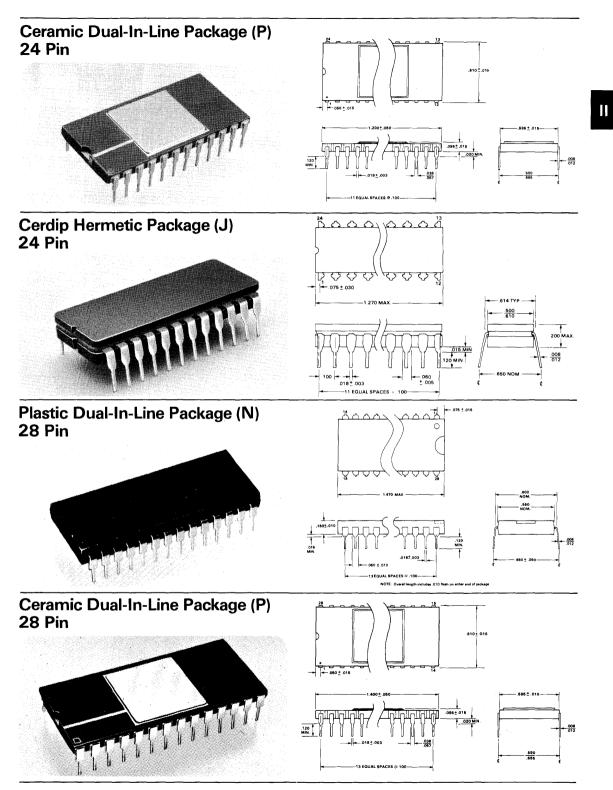

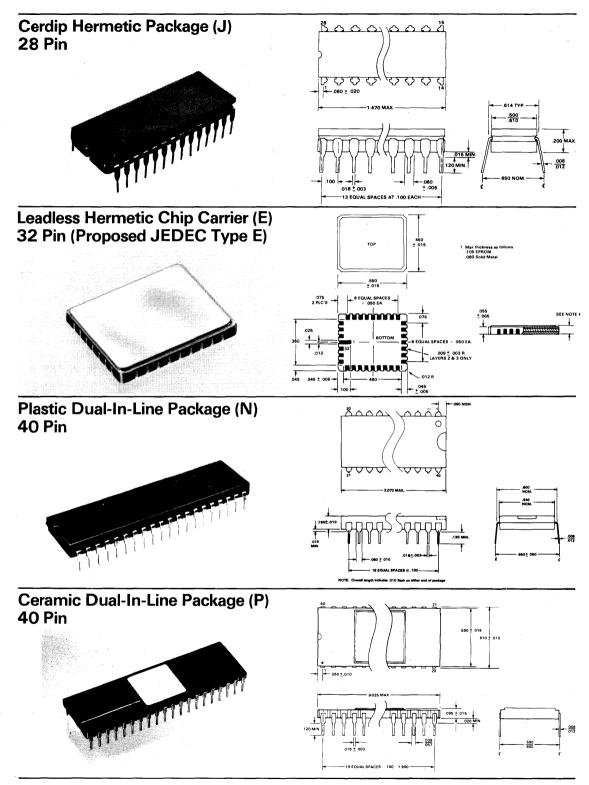

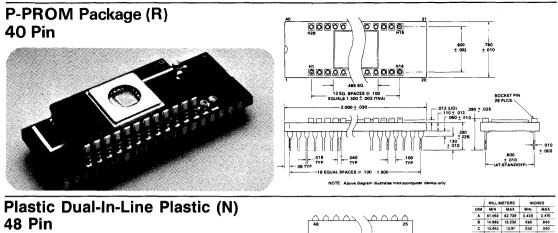

# PACKAGE DESCRIPTIONS

11-6

<u>م</u> ۵

0

مممم

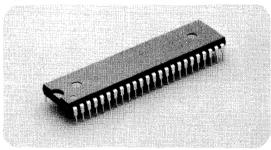

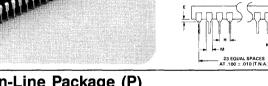

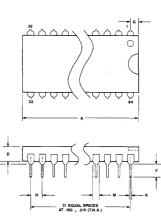

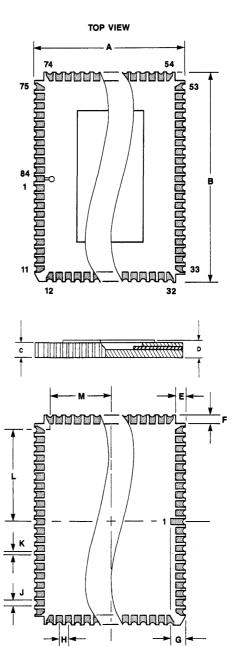

# Plastic Dual-In-Line Plastic (N) 48 Pin

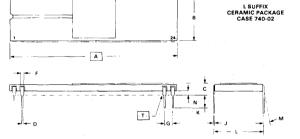

# Ceramic Dual-In-Line Package (P) 48 Pin

|     | MILLIM   | ETERS | INCHES    |       |

|-----|----------|-------|-----------|-------|

| DIM | MIN      | MAX   | MIN       | MAX   |

| A   | 60.35    | 61.57 | 2.376     | 2.424 |

| В   | 14.63    | 15.34 | 0.576     | 0.604 |

| С   | 3.05     | 4.32  | 0.120     | 0.160 |

| D   | 0.381    | 0.533 | 0.015     | 0.021 |

| F   | 0.762    | 1.397 | 0.030     | 0.055 |

| G   | 2.54 BSC |       | 0.100 BSC |       |

| J   | 0.203    | 0.330 | 0.008     | 0.013 |

| ĸ   | 2.54     | 4.19  | 0.100     | 0.165 |

| L   | 14.99    | 15.65 | 0.590     | 0.616 |

| м   | 0°       | 10°   | 0°        | 10°   |

| N   | 1.016    | 1.524 | 0.040     | 0.060 |

NOTES:

- 1. DIMENSION -A-IS DATUM.

- 2. POSITIONAL TOLERANCE FOR LEADS:

- Ø 0.25 (0.010) T AM

- 3. T-IS SEATING PLANE.

- 4. DIMENSION "L" TO CENTER OF LEADS WHEN FORMED PARALLEL.

- 5. DIMENSIONING AND TOLERANCING PER ANSI Y14.5, 1973.

14.986

16.256

13.462

13.97

3.555

4084

0.391

1.524

3048

3.81

1.524

2.286

1.186

1.734

15.24

3.031

0.203

0.305

1.143

1.775

.140 164 .120 .090

.600 70 .015 .008 .045 02

> D e L

# Plastic Dual-In-Line Plastic (N) 64 Pin

Γ

- 5. WHEN THE SOLDER LEAD FINISH IS SPECIFIED, THE MAXIMUM LIMIT SHALL BE INCREASED BY .003 IN. 4. MEASURED FROM CENTERLINE TO CENTERLINE AT LEAD TIPS. 3. PACKAGE STANDOFF TO BE MEASURED PER JEDEC REQUIREMENTS. 2. OVERALL LENGTH INCLUDES .010 IN. FLASH ON EITHER END OF THE PACKAGE. 1. LEAD FINISH IS TO BE SPECIFIED ON THE DETAIL SPECIFICATION.

NOTES;

| DIM. | INC   | INCHES |       |  |

|------|-------|--------|-------|--|

|      | MIN.  | MAX.   | NOTES |  |

| Α    | 3.180 | 3.230  | 2     |  |

| в    | .890  | .940   |       |  |

| С    | .790  | .810   |       |  |

| D    | .170  | .190   |       |  |

| E    | .020  | .060   | 3     |  |

| F    | .120  | .150   |       |  |

| G    | .040  | .070   |       |  |

| н    | .090  | .110   |       |  |

| J    | .900  | 1.000  | 4     |  |

| к    | .015  | .021   | 5     |  |

| L    | .008  | .012   | 5     |  |

| м    | .045  | .070   |       |  |

INCHES

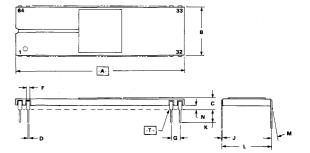

# 68000 Family Ceramic Dual-In-Line Package (P) 64 Pin

|     | MILLIM   | ETERS | INCHES    |       |

|-----|----------|-------|-----------|-------|

| DIM | MIN      | MAX   | MIN       | MAX   |

| Α   | 80.52    | 82.04 | 3.170     | 3.240 |

| В   | 22.25    | 22.96 | 0.900     | 0.920 |

| С   | 3.05     | 4.32  | 0.120     | 0.170 |

| D   | 0.38     | 0.53  | 0.015     | 0.021 |

| F   | 0.76     | 1.40  | 0.030     | 0.057 |

| G   | 2.54 BSC |       | 0.100 BSC |       |

| J   | 0.20     | 0.33  | 0.008     | 0.013 |

| ĸ   | 2.54     | 4.19  | 0.100     | 0.165 |

| r   | 22.61    | 23.11 | 0.890     | 0.910 |

| М   | -        | 10°   | -         | 10°   |

| N   | 1.02     | 1.52  | 0.020     | 0.060 |

#### NOTES:

- 1. Dimension-A-is datum.

- 2. Positional tolerance for leads: → 0.25 (0.010) → T A →

- 4. Dimension "L" to center of leads when formed parallel.

- 5. Dimensioning and tolerancing per ANSI Y14.5, 1973.

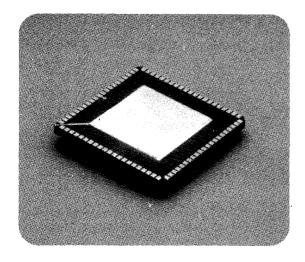

# Ceramic Leadless Chip Carrier (E) 84 Pin

BOTTOM

| DIM. | INC   | NOTES |       |

|------|-------|-------|-------|

|      | MIN.  | MAX.  | 10120 |

| A    | 1.138 | 1.167 |       |

| В    | 1.138 | 1.167 |       |

| C    | .070  | .090  |       |

| D    | .080  | .110  |       |

| E    | .044  | .056  |       |

| F    | .044  | .056  |       |

| G    | .075  | .095  |       |

| н    | .048  | .052  |       |

| н    | .048  | .052  |       |

| J    | .033  | .039  |       |

| к    | .010  | .018  |       |

| L    | .495  | .505  |       |

| м    | .495  | .505  |       |

NOTES

- 1.

- BODY MATERIAL SHALL BE A1203 PLATING SHALL BE GOLD OVER NICKEL AS SPECIFIED IN THE DETAIL SPECIFICATION 2.

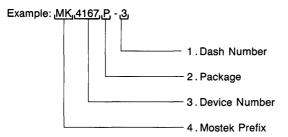

# **ORDERING INFORMATION**

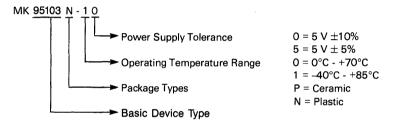

Factory orders for parts described in this book should include a four-part number as explained below:

1. Dash Number

One or two numerical characters defining specific device performance characteristics and operating temperature range.

### 2. Package

- P Gold side-brazed ceramic DIP

- J CER-DIP

- N Epoxy DIP (Plastic)

- K Tin-side-brazed ceramic DIP

- T Ceramic DIP with transparent lid

- E Ceramic leadless chip carrier

- D Dual density RAM-PAC

- F Flat pack

### 3. Device Number

| 1XXX or 1XXXX | - | Shift Register, ROM              |

|---------------|---|----------------------------------|

| 2XXX or 2XXXX | - | ROM, EPROM                       |

| 3XXX or 3XXXX | - | ROM, EPROM                       |

| 38XX          | - | Microcomputer Components         |

| 4XXX or 4XXXX | - | RAM                              |

| 5XXX or 5XXXX | - | Telecommunication and Industrial |

| 7XXX or 7XXXX | - | Microcomputer Systems            |

4. Mostek Prefix

MK - Standard Prefix

MKB - Military Hi-Rel screening to MIL-STD-883 Class B for extended temperature range operation.

MKI - Industrial Hi-Rel screening for -40°C to +85°C operation.

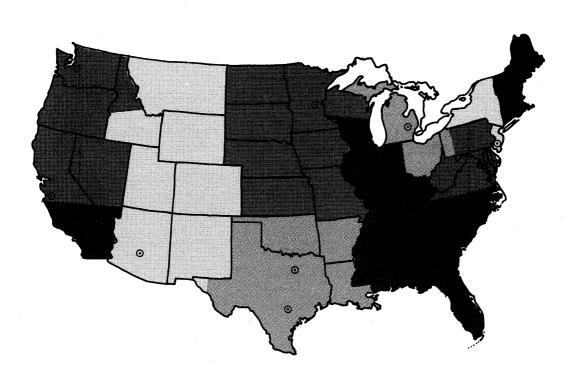

# **U.S. AND CANADIAN SALES OFFICES**

#### CORPORATE HEADQUARTERS

Mostek Corporation 1215 W. Crosby Rd. P.O. Box 110169 Carrollton, Texas 75006 214/466-6000 TWX 910-860-5975

#### **REGIONAL OFFICES**

Northeastern Area Mostek 777 West Putnam Greenwich, Conn. 06830 203/531-1146 TWX 710-579-2928

Northeast U.S. Mostek 83 Cambridge St. Suite 2-D Burlington, Mass. 01803 617/273-3310 TWX 710-348-0459

Southeastern Area Mostek Pavilions at Greentree Suite 101 Marlton, New Jersey 08053 609/596-9200 TWX 710-940-0103

#### Southeast U.S.

#### Mostek 13907 N. Dale Mabry Highway

Suite 201 Tampa, Florida 33618 813/962-8338 TWX 810-876-4611 Mostek 303 Williams Ave. Suite 1031

Huntsville, AL 35801 205/539-2061 TWX 910-997-0411

#### Upstate NY Region Mostek

Mostek 4651 Crossroads Park Dr., Suite 201 Liverpool, NY 13088 315/457-2160

TWX 710-545-0255 Chicago Region Mostek Two Crossroads of Commerce Suite 360 Rolling Meadows, III. 60008 312/577-9870

312/577-9870 TWX 910-291-1207 North Central U.S.

Mostek 6101 Green Valley Dr. Bloomington, Mn. 55438 612/831-2322 TWX 910-576-2802

#### Michigan

Mostek Orchard Hill Place 21333 Haggerty Road Suite 321 Novi, MI 48050 313/348-8360 TWX 810-242-1471

Central U.S. Mostek 4100 McEwen Road Suite 151 Dallas, Texas 75234 214/386-9340 TWX 910-860-5437

#### Southwest Region

Mostek 4100 McEwen Road Suite 237 Dallas, Texas 75234 214/386-9141 TWX 910-860-5437

Chevy Chase #4 7715 Chevy Chase Dr., Suite 116 Austin, TX 78752 512/458-5226 TWX 910-874-2007

#### Western Region Northern California

Mostek 1762 Technology Drive Suite 126 San Jose, Calif. 95110 408/287-5080 TWX 910-338-2219

#### Seattle Region

Mostek 1107 North East 45th St. Suite 411 Seattle, WA 98105 206/632-0245 TWX 910-444-4030

#### Southern California

Mostek 18004 Skypark Circle Suite 140 Irvine, Calif. 92714 714/250-0455 TWX 910-595-2513

#### Arizona Region

Mostek Camelback Arboleda Office Park 1661 E. Camelback Suite 179 Phoenix, AZ 85016 602/279-0713 TWX 910-957-4581

# **U.S. AND CANADIAN REPRESENTATIVES**

#### ALABAMA

Conley & Associates, Inc. 3322 Memorial Pkwy., S.W. Suite 19 Huntsville, AL 35801 205/882-0316 TWX 810-726-2159

ARIZONA Summit Sales 7825 E. Redfield Rd. Scottsdale, AZ 85260 602/998-4850 TWX 910-950-1283

CALIFORNIA CK Associates 8333 Clairemont Mesa Blvd. Suite 105 San Diego, CA 92111 619/279-0420

Quality Peripherals 1210 S. Bascom Ave. Suite 10 San Jose, CA 95128 408/559-3882

Quality Peripherals 17941 Skypark Circle Suite H Irvine, CA 92714 714/250-1033

COLORADO Waugaman Associate\* 4800 Van Gordon Wheat Ridge, CO 80033 303/423-1020 TWX 910-938-0750

CONNECTICUT New England Technical Sales 240 Pomeroy Ave. Meriden, CT 06450 203/237.8827 TWX 710-461-1126

FLORIDA Conely & Associates, Inc.\* P.O. Box 309 235 S. Central Oviedo, FL 32765 305/365-3283 TWX 810-856-3520

Conely & Associates, Inc. 4019 W. Waters Suite 2 Tampa, FL 33614 813/885-7658 TWX 810-876-9136

Conely & Associates, Inc. P.O. Box 700 1612 N.W. 2nd Avenue Boca Raton, FL 33432 305/395-6108 TWX 510-953-7548

Remtek, Inc. 728 Degan Drive Port St. Lucie, FL 33452 305/878-6771

\*Home Office

GEORGIA Conely & Associates, Inc. 3951 Pleasantdale Road Suite 201 Doraville, GA 30340 414/447-6992 TWX 810-766-0488

Remtek, Inc. 18 Perimeter Park Suite 100 Atlanta, GA 30341 404/453-4705

ILLINOIS Carlson Electronic Sales\* Associates, Inc. 600 East Higgins Road Elk Grove Village, IL 60007 312/956-8240 TWX 910-222-1819

Mar-Con Associates Inc. 4836 Main St. Skokie, IL 60077 312/675-6450 910-223-3645 Compucon 312/677-3230

INDIANA Technology Marketing\* Corp. 599 Industrial Drive Carmel, IN 46032 317844-8462 TWX 910-997-0194

Technology Marketing Corp. 3428 West Taylor St. Fort Wayne, IN 46804 219/432-5553

INXX 810-499-4111 IOWA Carlson Electronic Sales 204 Collins Road, N.E. Cedar Rapids, IA 52402 319/37-6341

#### KANSAS Rush & West Associates\* 107 N. Chester Street Olathe, KS 66061 913/764-2700 Wichita 316/683-0206 TWX 910-749-6404

TWX 910-222-1819

KENTUCKY Technology Marketing Corp. 8819 Roman Court P.O. Box 91147 Louisville, KY 40291 502/499-7808 TWX 810-535-3757

MARYLAND Arbotek Associates 102 W. Joppa Road Towson, MD 21204 301/825-0775 TWX 710-862-1874 KD Associates 201 Benton Avenue Linthicum, MD 21090 301/859-5151 (Baltimore Area) 301/261-1311 (Washington Area) TWX 710-862-9320

MASSACHUSETTS New England Technical Sales\* 101 Cambridge Street Burlington, MA 01803 617/272-0434 603/778-8495 (Home) TWX 710-332-0435

MICHIGAN Action Components 21333 Haggerty Road Suite 310B Novi, MI 48050 313/349-3940

Comp-U-Tronics, Inc. Route 2, Box 98 Blue Springs, MI 64015 816/229-3370

MINNESOTA Cahill, Schmitz & Cahill, Inc.\* 315 N. Pierce St. Paul, MN 55104 612/646-7217 TWX 910-563-3737

Dytec/North, Inc. 1821 University Ave. Suite 173 South St. Paul, MN 55104 612/645-5816 TWX 910-563-3724

Micro Resources, Inc. 4640 W. 77th St. Suite 109 Edina, MN 55435 612/830-1454

MISSOURI Rush & West Associates 720 Manchester Road Suite 211 Ballwin, MO 63011 314/394-7271 TWX 910-752-653

NORTH CAROLINA Conely & Associates, Inc. 4050 Wake Forest Road Suite 102 Raleigh, NC 27609 919/876-9862 TWX 510-928-1829

NEW JERSEY Datronix 1930 E. Mariton Pike Executive News, Suite P-79 Cherry Hill, NJ 08003 609/424-6622

Tritek Sales, Inc. 21 E. Euclid Ave. Haddonfield, NJ 08033 609/429-1551 215/627-0149 (Philadelphia Line) TWX 710-896-0881 NEW MEXICO Waugaman Associates P.O. Box 14894 Albuquerque, NM 871111

or 9004 Menaul NE Suite 7 Albuquerque, NM 87112 505/294-1436

NEW YORK ERA Inc. 354 Veterans Memorial Highway Commack, NY 11725 516/543-0510 TWX 510-226-1485 (New Jørsey Phone # 800/645-5500, 5501)

Tri-Tech Electronics Inc.\* 6836 East Genesse St. Fayetteville, NY 13066 315/446-2881 TWX 710-541-0604

Tri-Tech Electronics, Inc. 3215 East Main St. Endwell, NY 13760 607/754-1094 TWX 510-252-0891

Tri-Tech Electronics, Inc. 300 Main St. E. Rochester, NY 14445 716/385-6500 TWX 510-253-6356

Tri-Tech Electronics, Inc. 14 Westview Dr. Fishkill, NY 12524 914/897-5611 TWX 710-541-0604

OHIO The Lyons Corp. 4812 Frederick Rd. Dayton, Ohio 45414 513/278-0714 TWX 810-459-1754

The Lyons Corp. 4615 N. Streetsboro Rd. Richfield, Ohio 44286 216/659-9224 TWX 810-427-9103

OREGON Northwest Marketing Assoc. 9999 S.W. Wilshire St. Suite 124 Portland, OR 97225 503/297-2581 TELEX 910-464-5157

TEXAS Technological System Sales 4255 LBJ Freeway Suite 282 Dallas, TX 75234 214/458-0644

#### UTAH

Waugaman Associates 5258 Pinemont Dr. Suite B-100 Sait Lake City, UT 84107 801/261-0802 TLX 757949 WASHINGTON Northwest Marketing Assoc.\* 12835 Bellevue-Redmond Rd. Suite 330N Bellevue, WA 98005 206/455-5846 TWX 910-443-2445

WISCONSIN

Carlson Electronic\* Sales Associates, Inc. Northbrook Executive Ctr. 10701 West North Ave. Suite 12 Milwaukee, WI 53226 414/476-2790 TWX 910-222-1819

CANADA Cantec Representatives Inc.\* 1573 Laperriere Ave. Ottawa, Ontario Canada, K1Z 7T3 613/725-3704

Cantec Representatives Inc. 8 Strathearn Ave., Unit 18 Brampton, Ontario Canada LET 4L8 416/791-5922 TWX 610-492-2683

TWX 610-562-8967

Cantec Representatives Inc. 3639 Sources Blvd. Suite 116 Doilard Des Ormeaux, Quebec Canada H9B 2K4 514/683-6131 TWX 610-422-3985

PUERTO RICO

Jose L. Puig New England Technical Sales Corj PO. Box 8804 Ponce, Puerto Rico PR00732 809/843-7139

# **U.S. AND CANADIAN DISTRIBUTORS**

#### ALABAMA

Schweber Electronics 2227 Drake Avenue S.W. Suite 14 Huntsville, ALA 35805 205/882-2200

#### ARIZONA

Kierulff Electronics 4134 E. Wood St. Phoenix, AZ 85040 602/437-0750 TWX 910/951-1550 Schweber Electronics 11049 North 23rd Drive Phoenix, AZ 85029 602/97-4874 TWX 910/950-1174

#### CALIFORNIA

Arrow Electronics 2961 Dow Avenue Tustin, CA 92680 714/838-5422 TWX 910-595-2860 Arrow Electronics 19748 Dearborn St. Chatsworth, CA 91311 213/701-7500 TWX 910-483-2086

Arrow Electronics 9511 Ridgehaven Court San Diego, CA 92123

619/565-4800 TWX 310/371-8757 Arrow Electronics

521 Weddell Dr. Sunnyvale, CA 94086 408/745-6600

TWX 910/339-9371 Kierulff Electronics 2585 Commerce Way Los Angeles, CA 90040

Los Angeles, CA 900 213/725-0325 TWX 910/580-3106

Kierulff Electronics 3969 E. Bayshore Rd. Palo Alto, CA 94303

415/968-6292 TWX 910/379-6430

Kierulff Electronics 8797 Balboa Avenue San Diego, CA 92123

619/278-2112 TWX 910/335-1182 Kierulff Electronics

14101 Franklin Avenue Tustin, CA 92680 714/731-5711

TWX 910/595-2599 Schweber Electronics 17822 Gillette Avenue

Irvine, CA 92714 714/863-0200 TWX 910/595-1720

Schweber Electronics 3110 Patrick Henry Dr. Santa Clara, CA 95050 408/748-4700 TWX 910/338-2043

#### COLORADO

Arrow Electronics 1390 S. Potomac Street Suite 136 Aurora, CO 80012 303/696-1111 TWX 910/932-2999 Kierulff Electronics 7060 S. Tucson Way Englewood, CO 80112 303/790-4444 TWX 910/932-0169

#### CONNECTICUT

Arrow Electronics 12 Beaumont Rd. Wallingford, CT 06492 203/265-7741 TWX 710/476-0162 Kierulff Electronics 165 N. Plains Industrial Rd. Wallingford, CT 06492 203/265-1115 TWX 710/476-0450

Schweber Electronics Finance Drive Commerce Industrial Park Danbury, CT 06810 203/792-3500 TWX 710/456-9405

#### FLORIDA

Arrow Electronics 1001 N.W. 62nd St. Suite 108 Ft. Lauderdale, FL 33309 305/776-7790 TWX 510/955-9456 Arrow Electronics 50 Woodlake Dr. Palm Bay, FL 32905 305/725-1480 TWX 510/959-6337 Kierulff Electronics 4850 N. State Road 7 Suite E Ft. Lauderdale, FL 33319 305/486-4004 TWX 510/955-9801 Kierulff Electronics 3247 Tech Drive St. Petersburg, FL 33702 813/576-1966 TWX 810/863-5625 Schweber Electronics 2830 North 28th Terrace Hollywood, FL 33020 305/927-0511 TWX 510/954-0304 Schweber Electronics 181 Whooping Loop Altamonte Springs, FL 32701 (Orlando) 305/331-7555

#### GEORGIA

Arrow Electronics 2979 Pacific Drive Norcross, GA 30071 404/449-8252 TWX 810/766-0439

Kierulff Electronics 5824 E. Peachtree Corner East Norcross, GA 30092 404/447-5252 TWX 810/766-4527

Schweber Electronics 303 Research Drive, Suite 210 Norcross, GA 30092 404/449-9170 TWX 810/766-1592

#### ILLINOIS

Arrow Electronics 2000 Algonquin Road Schaumburg, IL 60195 312/397-3440 TWX 910/291-3544 Kierulff Electronics 1536 Landmeier Rd. Elk Grove Village, IL 60007 312/640-0200 TWX 910/222-0351 Schweber Electronics

904 Cambridge Dr. Elk Grove Village, IL 60007 312/364-3750 TWX 910/222-3453

#### INDIANA

Advent Electronics Electronics 8446 Moller Indianapolis, IN 46268 317/872-4910 TWX 810/341-3228

Arrow Electronics 2718 Rand Road Indianapolis, IN 46241 317/243-9353 TWX 810/341-3119 Pioneer Electronics 6408 Castleplace Drive Indianapolis, IN 46250 317/849-7300

TWX 810/260-1794

#### IOWA

Advent Electronics 682 58th Avenue Court South West Cedar Rapids, IA 52404 319/363-0221 TWX 910/525-1337 Arrow Electronics

1930 St. Andrews Dr., NE Cedar Rapids, IA 52402 319/395-7230 Schweber Electronics

5270 North Park Place, N.E. Cedar Rapids, IA 52402 319/373-1417

#### KANSAS

Schweber Electronics Wycliff Commercial Center 10300 West 103rd Street Suite 103 Building F Overland Park, KS 66214 913/492-2921

#### MARYLAND

Arrow Electronics 4801 Benson Avenue Baltimore, MD 21227 301/247-5200 TWX 710/236-9005

Kierulff Electronics 825 D. Hammonds Ferry Road Linthicum, MD 21090 301/636-5800 TWX 710/234-1971 Pioneer Electronics

9100 Gaither Road Gaithersburg, MD 20877 301/921-0660 TWX 710/828-0545

Schweber Electronics 9218 Gaither Rd. Gaitherbursg, MD 20877 301/840-5900 TWX 710/828-9749

MASSACHUSETTES Arrow Electronics Arrow Drive Woburn, MA 01801 617/933-8130 TWX 710/393-6770 Kierulff Electronics 13 Fortune Drive Billerica, MA 01865 617/935-5134 TWX 710/390-1449 Lionex Corporation

1 North Avenue Burlington, MA 01803 617/272-9400 TWX 710/332-1387

Schweber Electronics 25 Wiggins Avenue Bedford, MA 01730 617/275-5100 TWX 710/326-0268

#### MICHIGAN

Arrow Electronics 3810 Varsity Drive Ann Arbor, MI 48104 313/971-8220 TWX 810/223-6020 Pioneer Electronics 13485 Stamford Livonia, MI 48150 313/525-1800 TWX 810/242-3271

Schweber Electronics 12060 Hubbard Ave. Livonia, MI 48150 313/525-8100 TWX 810/242-2983

#### MINNESOTA

Arrow Electronics 5230 W. 73rd Street Edina, MN 55435 612/830-1800 TWX 910/576-3125 Klerulff Electronics 7667 Cahili Rd. Edina, MN 55435 612/941-7500 TWX 910/576-2721 Schweber Electronics 7424 W. 78th Street Edina, MN 5345 612/941-5280 WX 910/576-3167

#### MISSOURI

Arrow Electronics 2360 Schuetz Road St. Louis, MO 63141 314/567-6888 TWX 910764-0882 Kierulff Electronics 2608 Metro Park Bivd. Maryland Heights, MO 63043 314/739-0855 TWX 910/782-0721

Olive Electronics 9910 Page Blvd. St. Louis, MO 63132 314/426-4500 TWX 910/763-0720

Schweber Electronics 502 Earth City Expressway Suite 203 Earth City, MO 63045

314/739-0526 Semiconductor Spec 3805 N. Oak Trafficway Kansas City, MO 64116 816/452-3900 NEW HAMPSHIRE Arrow Electronic 1 Perimeter Rd.

Manchester, NH 03103 603/668-6968 TWX 710/220-1684 Schweber Electronics Farms Bld'g #2 1st Floor Kilton & South River Road Manchester, NH 03102 603/625-2550 TWX 710/220-7572

#### NEW JERSEY

Arrow Electronics 6000 Lincoln Drive East Mariton, NJ 08053 609/596-8000 TWX 710/897-0829 Arrow Electronics 2 Industrial Rd. Fairfield, NJ 07006 201/575-5300 TWX 710/734-4403 Kierulff Electronics 37 Kulick Road Fairfield, NJ 07006 201/575-6750 TWX 710/734-4372 Schweber Electronics 18 Madison Road Eairfield NJ 07006 201/227-7880 TWX 710/734-4305

#### NEW MEXICO

Arrow Electronics 2460 Alamo Ave. S.E. Albuquerque, NM 87106 505/243-4566 TWX 910/989-1679

#### NEW YORK

Add Electronic 7 Adler Drive E. Syracuse, NY 13057 315/437-0300 Arrow Electronics 25 Hub Drive

Melville, NY 11747 516/391-1300 TWX 510/224-6155

Arrow Electronics 7705 Maltiage Drive P.O. Box 370 Liverpool, NY 13088 315/652-1000

TWX 710/545-0230 Arrow Electronics

3000 S. Winton Road Rochester, NY 14623 716/427-0300 TWX 510/253-4766

Arrow Electronics 20 Oser Ave.

Hauppauge, NY 11787 516/231-1000 TWX 510/227-6623

Lionex Corporation 400 Oser Ave. Hauppauge, NY 11787 516/273-1660 TWX 510/227-1042

Schweber Electronics 3 Town Line Circle Rochester, NY 14623 716/424-2222

Schweber Electronics 34 Jericho Turnpike Westbury, NY 11590 516/334-7474

516/334-7474 TWX 510/222-3660

# **U.S. AND CANADIAN DISTRIBUTORS**

#### NORTH CAROLINA

Arrow Electronics 938 Burke St. Winston Salem, NC 27102 919/725-8711 TWX 510/931-3169

Arrow Electronics 3117 Poplarwood Court Suite 123, P.O. Box 95163 Raleigh, NC 27625 919/876-3132 TWX 510/928-1856

Hammond Electronics 2923 Pacific Avenue Greensboro, NC 27406 919/275-6391 TWX 510/925-1094

Kierulff Electronics 1 North Commerce Center 5249 North Blv'd. Raleigh, NC 27604 919/872-8410 TWX 310/377-2204

Schweber Electronics 1 Commerce Center 5285 North Blv'd. Raleigh, NC 27604 919/876-0000 TWX 510/928-0531

#### OHIO

Arrow Electronics 7620 McEwen Road Centerville, OH 45459 513/435-5563 TWX 810/459-1611

Arrow Electronics 6238 Cochran Road Solon, OH 44139 216/248-3990 TWX 810/427-9409

Kierulff Electronics 23060 Miles Road Cleveland, OH 44128 216/587-6558 TWX 810/427-2282

Pioneer Electronics 4800 East 131st Street Cleveland, OH 44105 216/587-3600 TWX 810/422-2211

Pioneer Electronics 4433 Interpoint Blvd. Dayton, OH 45424 513/236-9900 TWX 810/459-1622

Schweber Electronics 23880 Commerce Park Road Beachwood, OH 44122 216/464-2970 TWX 810/427-9441 Schweber Electronics 7865 Paragon Road Suite 210 Dayton, OH 45459 513/439-1800

#### OKLAHOMA

Arrow Electronics 4719 S. Memorial Tulsa, OK 74745 918/665-7700 Kierulff Electronics 12318 E. 60th St. Tulsa, OK 74145 918/252-7537 TWX 910/845-2150 Quality Components 9934 East 21st South Tulsa, OK 74129 918/664-8812 Schweber Electronics 4815 South Sheridan Fountain Plaza Suite 109 Tulsa, OK 74145

#### 918/622-8000 OREGON

Arrow Electronics 10160 S.W. Nimbus Ave., F-3 Portland, OR 97223 503/684-1690

PENNSYLVANIA Arrow Electronics 850 Seco Rd. Monroeville, PA 15146 412/855-7000 TWX 710/797-3894 Pioneer Electronics 259 Kappa Drive Pittsburgh, PA 15238 412/782-2300 TWX 710/795-3122 Pioneer Electronics 261 Gibraltar Horsham, PA 19044 215/674-4000

215/674-4000 TWX 510/665-6778 Schweber Electronics 231 Gibraltar Rd. Horsham, PA 19044 215/441-0600 TWX 510/665-6778

Schweber Electronics 1000 R.I.D.C. Plaza Suite 203 Pittsburgh, PA 15238 412/782-1600 SOUTH CAROLINA Hammond Electronics 1035 Lowndes Hill Rd. Greenville, SC 29602 803/233-4121 TWX 810/281-2233

TEXAS Arrow Electronics 10125 Metropolitan Dr. Austin, TX 78758 512/835-4180 TWX 910/874-1348 Arrow Electronics 13715 Gamma Road Dallas, TX 75240 214/386-7500 TWX 910/860-5377 Arrow Electronics 10899 Kinghurst Drive Suite 100 Houston, TX 77099 713/530-4700 TWX 910/880-4439 **Kierulff Electronics** 3007 Longhorn Blv'd. Suite 105 Austin, TX 78758 512/835-2090 TWX 910/874-1359 Kierulff Electronics 9610 Skillman Ave. Dallas, TX 75243 214/343-2400 TWX 910/861-9149 **Kierulff Electronics** 10415 Landsbury Dr. Suite 210 Houston, TX 77099 713/530-7030 TWX 910/880-4057 **Quality Components** 4257 Kellway Circle Addison, TX 75001 214/387-4949 TWX 910/860-5459 Quality Components 2427 Rutland Drive Austin, TX 78758 512/835-0220

Quality Components 1005 Industrial Blv'd. Sugarland, TX 77478 713/491-2255 TWX 910/880-4893

TWX 910/874-1377

Schweber Electronics 4202 Beltway Drive Dallas, TX 75234 214/661-5010 TWX 910/860-5493 Schweber Electronics 6300 La Calma Dr. Suite 240 Austin, TX 78752 512/458-8253 Schweber Electronics 10625 Richmond Suite 100 Houston, TX 77042 713/784-3600 TWX 910/881-4836

#### UTAH

Arrow Electronics 4980 Amelia Earhart Dr. Salt Lake City, UT 84116 801/539-1135 Kierulff Electronics 2121 South 3600 West Salt Lake City, UT 84119 801/973-6913 TWX 910/925-4072

WASHINGTON Arrow Electronics 14320 NE 21st Bellevue, WA 98005 206/43-4800 TWX 910/444-3033 Kierulff Electronics 1053 Andover Park East Tukwila, WA 98188 206/575-4420 TWX 910/444-2034

WISCONSIN Arrow Electronics 434 Rawson Avenue Oak Creek, WI 53154 41/764-6600 TWX 910/262-1193 Kierulf Electronics 2236 G.W. Bluemound Road Waukesha, WI 53186 41/7784-8160 TWX 910/265-3653 Schweber Electronics 150 Sunnystope Road

Suite 120 Brookfield, WI 53005 414/784-9020

CANADA Preico Electronics 7611 Bath Road Mississauga, Ontario Toronto L4T 3T1 416/678-0401 Telex 06-96-8915

480 Port Royal St. W. Montreal 357 P.Q. H3L 2B9 514/389-8051 Telex 05-82-7590 Prelco Electronics 215 Stafford Road Nepean, Ontario K2E 7K1 613/726-1800 R.A.E. Industrial 3455 Gardner Court Burnaby, B.C. V5G 4J7 604/291-8866 TWX 610/929-3065 B.A.E. Industrial 11680 170th Street Edmonton, Alberta T5S 1J7 403/451-4001 Telex 037-2653 Zentronics 155 Colonnade Rd. Nepean, Ontario K2F7K1 613/226-8840 Zentronics 8 Tilbury Court Brampton, Ontario (Toronto) L6V 2L1 416/451-9600 Telex 06-97678 Zentronics 505 Locke St. St. Laurent, Quebec H4T IY7 514/735-5361 Telex 058-27535 Zentronics 590 Berry Street Winnipeg, Manitoba R3H 0S1 204/775-8661 Zentronics 564/10 Weber Street, N Waterloo, Ontario N2L 5C6 519/884-5700 Zentronics 11400 Brideport Road Unit 108 Richmond, BC V6X IT2 604/273-5575 Zentronics

Preico Electronics

291101105 3300-14 Avenue, N.E. Bay #1 Calgary, Alberta T2A 6J4 403/272-1021

\*Franchised for USA and Canada excluding California for military products

# INTERNATIONAL SALES REPRESENTATIVES AND DISTRIBUTORS

#### ARGENTINA

Rayo Electronics S.R.L. Belgrano 990, Pisos 6y2 1092 Buenos Aires, Republic of Argentina (38)-1779, Telex: 122153 ANS BK RAYO

#### AUSTRALIA

Amtron Tyree Pty. Ltd. 176 Cope Street Waterloo, N.S.W. 2017 Australia (02) 69-89.666 Telex: 25643 ANS BK TYREE

#### BRAZIL

Cosele, Ltd. Rua da Consolachao, 867 2 and Conj 22 01301 Sao Paulo - Sp, Brazil (11) 259 3719/255 1733 Telex: 1130869 ANS EK CSLE BR

#### HONG KONG CET 1402 Tung Wah Mansion 199 - 203 Hennessy Road Wanchai, Hong Kong (5) 729 376 Telex: 85148 ANS BK CET HX

ISRAEL

Telsys Ltd. 12 Kehilat Venetsia St. 69010 Tel-Aviv, Israel (3) 494891-2, 494881-2 Telex: 032392

#### JAPAN

Systems Marketing, Inc. Shin - kanda Bidg. 1-8-5 Kaji-cho Chiyoda-ku Tokyo 101, Japan 32542751 Telex: 25276 ANS BK SMITOK FAX 3 254 3288 Tomen Electronics Corp. 2-11 Uchisaiwai - Cho Chiyoda - Ku Tokyo, Japan 100 (03) 506 3670 Telex: J23548 ANS BK TMELC

#### KOREA

Vine Overseas Trading Corp. Room 308 Korea Electric Association Bldg. 11-4, Supyo-Dong, Jung-Ku CPO Box 3154 Seoul, Korea (02) 266 1663 Teler: K24154 ANS BK VINE O

Seoul Corp LTD. CPO Box 5003 Seoul 100, Korea (02) 752 6121 FAX (02) 754 1348 Telex: K28641 ANS BK SJLEE NEW ZEALAND E.C.S. Div. of Airspares P.O. Box 1048 Airport Palmerston North, New Zealand (63) 77-407 Telex: 791 3766 ANS BK Airspare 3766 NZ

#### SINGAPORE

Dynamar International, LTD. 12 Lorong Bakar Batu Unit 05-11 Kolam Ayer-Industrial Park, Singapore 1334 7476188 TLX RS26283 ANS BK DYNAMA FAX 7472649

#### SOUTH AFRICA Promilect P.O. Box 56310 Pinegowrie, 2123, Transvaal 789-1400 Telex: 424822

#### TAIWAN

Dynamar Taiwan Ltd. P.O. Box 67 - 445 Taipei, Taiwan (2) 541 8251 Telex: 11064 ANS BK 11064 DYNAMAR

#### FOR ALL OTHER COUNTRIES

Mostek Corporation International Dept. MS 2220 P.O. Box 110169 Carrollton, Texas 75006, USA 214/466-6000 Telex: 4630093 ANS BK MSTA FAX 466 7602

# INTERNATIONAL MARKETING OFFICES

#### EUROPEAN HEAD OFFICE Mostek International Av de Tervuren 270-272 Bte 21 B-1150 Brussels/Belgium 02/762, 18.80

02/762.18.80 Telex: 62011

### FRANCE

Mostek France s.a.r.l. 35 Rue de Montjean Z.A.C. Sud, Sentiers 504 F-94266 Fresnes Cedex (1)666.21.25 Telex: 204049

#### GERMANY PLZ 1-5 Mostek GmbH Friedlandstrasse 1 D-2085 Quickborn (04106) 2077/78 Telex: 213685

PLZ 6-7 Mostek GmbH Schurwaldstrasse 15 D-7303 Neuhausen/Filder (07158) 66.45 Telex: 72.38.86

PLZ 8 **Mostek GmbH** Freischutzstrasse 92 D-8000 Munchen 81 (089) 95.10.71 Telex: 5216516

#### IRELAND

Mostek Ireland B.V. Irish Sales Office Snugboro Industrial Park Blanchardstown, Co. Dublin (1) 217333 Telex: 30958

#### ITALY

Mostek Italia SRL Via F.D. Guerrazzi 27 1-20145 Milano (02) 318.5337/349.2696 and 34.23.89 Telex: 333601

#### SWEDEN Mostek Scandinavia AB Spjutvagen 7

S-17561 Jarfalla Sweden 08-362820 Telex: 12997

#### UNITED KINGDOM

Mostek U.K. Ltd. Masons House, 1-3 Valley Drive Kingsbury Road London, N.W.9 01-2049322 Telex: 25940

#### JAPAN

Mostek Japan KK 3 - 24 Sakuragaoka - Machi Shibuya - ku Tokyo 150 (03) 496 4221 TLX 78123686 ANS BK MKJAPAN FAX (03) 496 4787

#### FAR EAST

Mostek Asia LTD Suite 613 - 617 Mount Parker House 1111 Kings Road Hong Kong Phone: 5-681157-9 Telex: 72585 MKHK HX FAX 5 - 665450

II-19

# EUROPEAN SALES REPRESENTATIVES AND DISTRIBUTORS

#### AUSTRIA

Transistor Vertreibsges, mbH Auhofstrasse 41 A A-1130 Vienna (0222) 829451, 829404 Telex: 0133738

#### DENMARK

Semicap APS Alhambravej 3 DK-1826 Kobenhavn V 01-22.15.10 Telex: 15987

FINLAND Insele Oy Kumpulantie 1 SF-00520 Helsinki 52 90-750.600 Telex: 122217

#### FRANCE

Copel Rue Fourny, Z.I. B.P. 22, F-78530 BUC (1) 956 10.18 Telex: 698965

Facen 110 Av de Flandre F59290 Wasquehal. Nord (20) 98.92.15

Branch Offices in: Lille, Lyon, Nancy, Rouen, Strasbourg

Mecodis 33-35, Rue Pierre Brossolette F-94000 Creteil (1) 898.-1111 Telex: 231160 P.E.P. 541, Av. du General de Gaulle F-92140 Clamart (1)630.24.56 Telex: 204534

Scaib 80 Rue d'Arcueil SILIC 137 F-94523 Rungis Cedex (1)-687.23.13 Telex: 204674 *Branch offices:* Blanquefort, La Madeleine, Lyon, Meylan, Nantes

Sorhodis 150-152, Rue A. France F-69100 Villeurbanne (7) 855 0044 Telex: 380181

#### GERMANY Dr Dohrenberg Bayreuther Strasse 3 D-1000 Berlin 30 (030) 213.80.43 Telex: 0184860

Retron GmbH Rodeweg 18 Postfach 3143 3400 Goettingen (0551) 9040 Telex: 96733

Branch Offices in: Hannover, Frankfurt, Stuttgart, Krailling

Raffel-Electronic GmbH Lochnerstrasse 1 D-4030 Ratingen 1 (02102) 280.24 Telex: 8585180 Ecker Koenigsberger Strasse 2 D-6120 Michelstadt (06061) 2233 Telex: 4191630

POSITRON GmbH Benzstrasse 1 Postfach 100364 D-7016 Gerlingen/Stuttgart (07156) 3560 Telex: 7245266 Branch Offices in: Hamburg. Dusseldorf. Munchen

Matronic GmbH Lichtenberger Weg 3 D-7400 Tubingen (07071) 45031 Telex: 17707111

Dema-Electronic GmbH Turkenstrasse 11 D-8000 Munchen 2 (089) 2724053 Telex: 0529345

ITALY Comprel S.p.A. via le Fulvio Testi 115 1-20092 Cinisello B. (Mi) (02) 61.20.641/2/3/4/5 Telex: 332484

Branch Offices in: Bologna, Civitanova Marche, Firenze, Vicenza, Roma, Torino

Kontron S.p.A. Via Medici del Vascello.26 1-20138 Milano (02) 50721 Telex: 312288

Branch Offices in: Padova, Torino, Modena, Roma, Genova THE NETHERLANDS Nijkerk Elektronika BV Drentestraat 7 NL - 1083 HK Amsterdam (020) 462221 Telex: 11625

NORWAY Satt Electronics A/S PO. Box 70 O.H. Bangs Vei 17 N-1322 Hovik 02-12.36.00 Telex: 72558

PORTUGAL Digicontrole LDA Av. de Roma 105 Sexto Esquerdo 1700 Lisboa (19) 923924 Telex: 15084

SPAIN Comeita S.A. Emilio Munoz 41, ESC 1 Planta 1 Nave 2 Madrid-17 (01) 754 3001 Telex: 42007

Branch Office: C. Pedro IV, 84-5<sup>a</sup> Planta Barcelona 5 (03) 300-7712 Telex: 51934

#### SWEDEN

Nordisk Elektronik AB Box 27301 S-102 54 Stockholm 08-6350 40 Telex: 10547

### SWITZERLAND

Memotec AG Gaswerkstrasse, 32 CH-4901 Langenthal 063-28.11.22 Telex: 68636

UNITED KINGDOM

Celdis Limited 37-39 Loverock Road Reading Berks RG 31 ED 0734-58.51.71 Telex: 8483770

Hill Electronics 290 Antrim Road Belfast (0232) 755611 Telex: 747103

Pronto Electronic Systems Ltd 466-478 Cranbrook Road, Gants Hill, Ifford Essex IG2 6LE 01-554 62.22 Telex: 8954213

VSI Electronics (UK) Ltd. Roydonbury Industrial Park Horsecróft Road Harlow, Essex CM195 BY (0279) 35477 Telex: 81387

Thame Components Ltd. Thame Park Road Thame, Oxon OX9 3XD 084 421.31.46 Telex: 837917

# 1984/1985 MICROELECTRONIC DATA BOOK

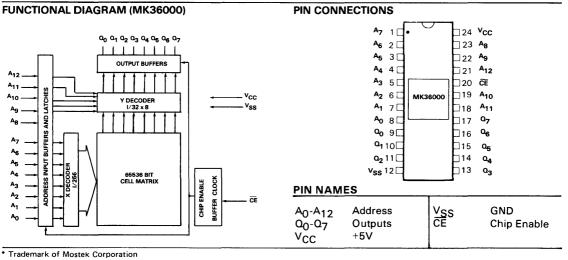

## 64K-BIT READ-ONLY MEMORY MK36000(P/J/N) SERIES

#### FEATURES

- MK36000 8K x 8 Organization—

"Edge Activated" \* operation (CE)

- □ Access Time / Cycle Time

| P/N       | Access | Cycle  |

|-----------|--------|--------|

| MK36000-4 | 250 ns | 375 ns |

| MK36000-5 | 300 ns | 450 ns |

$\Box$  Single +5V ± 10% Power Supply

#### DESCRIPTION

The MK36000 is a N-channel silicon gate MOS Read Only Memory, organized as 8192 words by 8 bits. As a state-ofthe-art device, the MK36000 incorporates advanced circuit techniques designed to provide maximum circuit density and reliability with the highest possible performance, while maintaining low power dissipation and wide operating margins.

Use of a static storage cell with clocked control periphery allows the circuit to be put into an automatic low power standby mode. This is accomplished by maintaining the chip

- □ Standard 24 pin DIP

- Low Power Dissipation 220mW Max Active

- □ Low Standby Power Dissipation 45mW Max, (CE High)

- On chip latches for addresses

- Inputs and three-state outputs TTL compatible

- Outputs drive 2 TTL loads and 100pF

- MKB version screened to MIL-STD-883

enable ( $\overline{CE}$ ) input at a TTL high level. In this mode, power dissipation is reduced to typically 45mW, as compared to unclocked devices which draw full power continuously. In system operation, a device is selected by the  $\overline{CE}$  input, while all others are in a low power mode, reducing the overall system power. Lower power means reduced power supply cost, less heat to dissipate and an increase in device and system reliability.

The edge activated chip enable also means greater system flexibility and an increase in system speed.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Any Terminal Relative to V <sub>SS</sub> | 1.0 V to +7 V                |

|-----------------------------------------------------|------------------------------|

| Operating Temperature T <sub>A</sub> (Ambient)      | $\dots 0^{\circ}$ C to +70°C |

| Storage Temperature - Ceramic (Ambient)             | 65°C to +150°C               |

| Storage Temperature - Plastic (Ambient)             | 55°C to +125°C               |

| Power Dissipation                                   | 1 Watt                       |

|                                                     |                              |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED DC OPERATING CONDITIONS<sup>6</sup>**

$(0^{\circ}C \le T_{A} \le +70^{\circ}C)$

| SYM             | PARAMETER             | MIN  | ТҮР | MAX             | UNITS | NOTES |

|-----------------|-----------------------|------|-----|-----------------|-------|-------|

| V <sub>cc</sub> | Power Supply Voltage  | 4.5  | 5.0 | 5.5             | V     | 6     |

| V <sub>IL</sub> | Input Logic 0 Voltage | -1.0 |     | 0.8             | V     |       |

| V <sub>IH</sub> | Input Logic 1 Voltage | 2.0  |     | V <sub>CC</sub> | V     |       |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%) (0^{\circ}C \le T_A \le +70^{\circ}C)^{6}$

| SYM               | PARAMETER                                                | MIN | ТҮР | MAX | UNITS | NOTES |

|-------------------|----------------------------------------------------------|-----|-----|-----|-------|-------|

| I <sub>CC1</sub>  | V <sub>CC</sub> Power Supply Current (Active)            |     |     | 40  | mA    | 1     |

| I <sub>CC2</sub>  | V <sub>CC</sub> Power Supply Current (Standby)           |     |     | 8   | mA    | 7     |

| I <sub>I(L)</sub> | Input Leakage Current                                    | -10 |     | 10  | μA    | 2     |

| I <sub>O(L)</sub> | Output Leakage Current                                   | -10 |     | 10  | μA    | 3     |

| V <sub>OL</sub>   | Output Logic "O" Voltage<br>@ I <sub>OUT</sub> = 3.3 mA  |     |     | 0.4 | V     | -     |

| V <sub>OH</sub>   | Output Logic "1" Voltage<br>@ I <sub>OUT</sub> = −220 μA | 2.4 |     |     | V     |       |

#### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%) (0^{\circ}C \le T_A \le +70^{\circ}C)^6$

| SYM              |                                     |     | -4    |     | -5    |       | 1     |

|------------------|-------------------------------------|-----|-------|-----|-------|-------|-------|

|                  | PARAMETER                           | MIN | MAX   | MIN | MAX   | UNITS | NOTES |

| t <sub>C</sub>   | Cycle Time                          | 375 |       | 450 |       | ns    | 4     |

| t <sub>CE</sub>  | CE Pulse Width                      | 250 | 10000 | 300 | 10000 | ns    | 4     |

| t <sub>AC</sub>  | CE Access Time                      |     | 250   |     | 300   | ns    | 4     |

| t <sub>OFF</sub> | Output Turn Off Delay               |     | 60    |     | 75    | ns    | 4     |

| t <sub>AH</sub>  | Address Hold Time Referenced to CE  | 60  |       | 75  |       | ns    |       |

| t <sub>AS</sub>  | Address Setup Time Referenced to CE | 0   |       | 0   |       | ns    |       |

| tp               | CE Precharge Time                   | 125 |       | 150 |       | ns    |       |

#### NOTES:

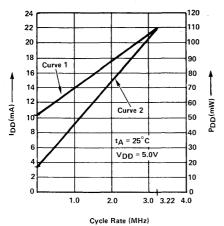

1. Current is proportional to cycle rate. I<sub>CC1</sub> is measured at the specified minimum cycle time. Data Outputs open.

2. VIN = 0 V to 5.5 V (V<sub>CC</sub> = 5.V)

3. Device unselected; V<sub>OUT</sub> = 0 V to 5.5 V

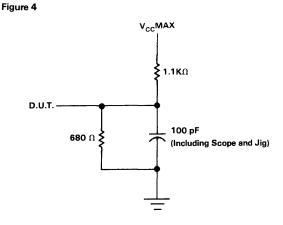

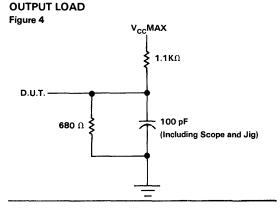

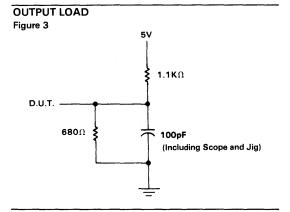

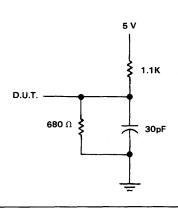

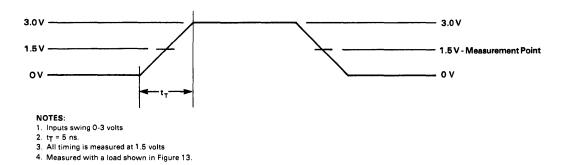

4. Measured with 2 TTL loads and 100 pF, transition times = 20 ns

5. Capacitance measured with Boonton Meter or effective capacitance  $C = \Delta Q$  with  $\Delta V = 3$  volts calculated from the equation:

6. A minimum 2 ms time delay is required after the application of V<sub>CC</sub> (+5). before proper device operation is achieved.  $\overline{\text{CE}}$  must be at  $\text{V}_{\text{IH}}$  for this time period. 7. CE high

#### CAPACITANCE

$(0^{\circ}C \le T_{A} \le 70^{\circ}C)$

| SYM            | PARAMETER          | ТҮР | MAX | UNITS | NOTES |

|----------------|--------------------|-----|-----|-------|-------|

| C <sub>l</sub> | Input Capacitance  | 5   | 8   | pF    | 5     |

| C <sub>O</sub> | Output Capacitance | 7   | 15  | pF    | 5     |

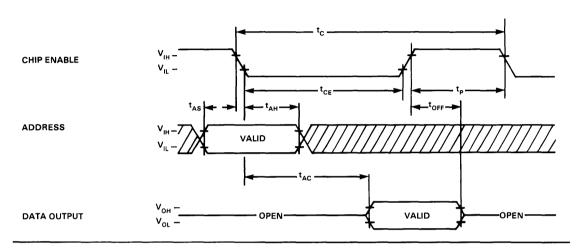

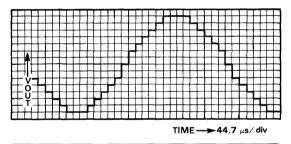

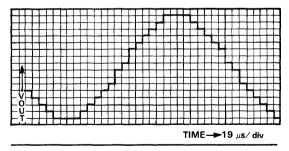

#### TIMING DIAGRAM

#### **DESCRIPTION** (Continued)

The MK36000 features onboard address latches controlled by the  $\overline{CE}$  input. Once the address hold time specification has been met, new address data can be applied in anticipation of the next cycle. Outputs can be wire 'OR'ed together, and a specific device can be selected by utilizing the  $\overline{CE}$  input with no bus conflict on the outputs. The  $\overline{CE}$ input allows the fastest access times yet available in 5 volt only ROM's and imposes no loss in system operating flexibility over an unclocked device.

Other system oriented features include fully TTL compatible inputs and outputs. The three state outputs, controlled by the  $\overline{CE}$  input, will drive a minimum of 2 standard TTL loads. The MK36000 operates from a single +5 volt power supply with a wide  $\pm 10\%$  tolerance, providing the widest operating margins available. The MK36000 is packaged in the industry standard 24 pin DIP.

Any application requiring a high performance, high bit density ROM can be satisfied by the MK36000 ROM. This device is ideally suited for 8 bit microprocessor systems such as those which utilize the Z80. It can offer significant cost advantages over PROM.

#### OPERATION

The MK36000 is controlled by the chip enable ( $\overline{CE}$ ) input. A negative going edge at the  $\overline{CE}$  input will activate the device as well as strobe and latch the inputs into the on-chip address registers. At access time the outputs will become active and contain the data read from the selected location. The outputs will remain latched and active until  $\overline{CE}$  is returned to the inactive state.

.

111-4

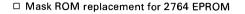

## 64K-BIT MOS READ-ONLY MEMORY MK37000(P/J/N) SERIES

#### FEATURES

- Organization; 8K x 8 Bit ROM JEDEC Pinout

- □ Pin compatible with Mostek's BYTEWYDE<sup>™</sup> Memory Family

#### Access Time/Cycle Time

| P/N       | ACCESS | CYCLE  |  |

|-----------|--------|--------|--|

| MK37000-5 | 300 ns | 450 ns |  |

| MK37000-4 | 250 ns | 375 ns |  |

#### DESCRIPTION

The MK37000 is a N-channel silicon gate MOS Read Only Memory, organized as 8192 words by 8 bits. As a state-of-the-art device, the MK37000 incorporates advanced circuit techniques designed to provide maximum circuit density and reliability with the highest possible performance, while maintaining low power dissipation and wide operating margins. The MK37000 is to be used as a pin/function compatible mask programmable alternative to the 2764 8K x 8 bit EPROM. As a member of the Mostek BYTEWYDE

- □ No Connections allow easy upgrade to future generation higher density ROMs

- □ Low power dissipation: 220mW max active, 45mW max standby

- □ CE and OE functions facilitate Bus control

- □ MKB version screened to MIL-STD-883

Memory Family, the MK37000 brings to the memory market a new era of ROM, PROM and EPROM compatibility previously unavailable.

Use of clocked control periphery and a standard static ROM cell makes the MK37000 the lowest power 64K ROM available. Active power is a mere 220mW while standby ( $\overline{CE}$  high) is only 45mW. To provide greater system flexibility an output enable ( $\overline{OE}$ ) function has been added using one of the extra pins available on the

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Any Terminal Relative to V <sub>SS</sub>                                                                        | 1.0V to +7V                      |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Operating Temperature T <sub>A</sub> (Ambient)                                                                             | 0°C to +70°C                     |

| Storage Temperature—Ceramic (Ambient)                                                                                      |                                  |

| Storage Temperature—Plastic (Ambient)                                                                                      | –55°C to +125°C                  |

| Power Dissipation                                                                                                          | 1 Watt                           |

| *Stresses greater than those listed under "Absolute Maximum Patings" may cause permanent damage to the davide. This is a s | troop rating only and functional |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED DC OPERATING CONDITIONS<sup>6</sup>**

$(0^{\circ}C \le T_{A} \le +70^{\circ}C)$

| SYM | PARAMETER             | MIN  | ТҮР | MAX             | UNITS | NOTES |

|-----|-----------------------|------|-----|-----------------|-------|-------|

| Vcc | Power Supply Voltage  | 4.5  | 5.0 | 5.5             | v     |       |

| VIL | Input Logic 0 Voltage | -1.0 |     | 0.8             | v     |       |

| VIH | Input Logic 1 Voltage | 2.0  |     | V <sub>CC</sub> | v     |       |

#### DC ELECTRICAL CHARACTERISTICS 6

$(V_{CC} = 5V \pm 10\%) (0^{\circ}C \le T_A \le +70^{\circ}C)$

| SYM               | PARAMETER                                               | MIN | ТҮР | MAX | UNITS | NOTES |

|-------------------|---------------------------------------------------------|-----|-----|-----|-------|-------|

| ICC1              | V <sub>CC</sub> Power Supply Current (Active)           |     | 1   | 40  | mA    | 1     |

| I <sub>CC2</sub>  | V <sub>CC</sub> Power Supply Current<br>(Standby)       |     |     | 8   | mA    | 7     |

| l <sub>l(L)</sub> | Input Leakage Current                                   | -10 |     | 10  | μA    | 2     |

| IO(L)             | Output Leakage Current                                  | -10 |     | 10  | μΑ    | 3     |

| V <sub>OL</sub>   | Output Logic "O" Voltage<br>@ I <sub>OUT</sub> = 3.3mA  |     |     | 0.4 | V     |       |

| V <sub>OH</sub>   | Output Logic "1" Voltage<br>@ I <sub>OUT</sub> = -220μA | 2.4 |     |     | V     |       |

#### **AC ELECTRICAL CHARACTERISTICS<sup>6</sup>**

$(V_{CC} = 5V \pm 10\%) (0^{\circ}C \le T_A \le +70^{\circ}C)$

| SYM              |                                     | -   | 4      | -5  |        |       |       |  |

|------------------|-------------------------------------|-----|--------|-----|--------|-------|-------|--|

|                  | PARAMETER                           | MIN | MAX    | MIN | MAX    | UNITS | NOTES |  |

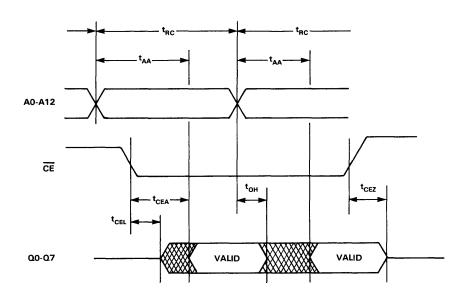

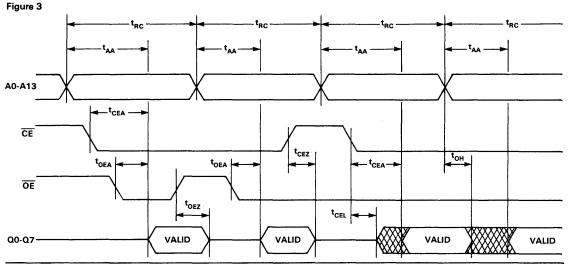

| <sup>t</sup> RC  | Read Cycle Time                     | 375 |        | 450 |        | ns    | 4     |  |

| <sup>t</sup> CE  | CE Pulse Width                      | 250 | 10,000 | 300 | 10,000 | ns    | 4     |  |

| <sup>t</sup> CEA | CE Access Time                      |     | 250    |     | 300    | ns    | 4     |  |

| <sup>t</sup> CEZ | Chip Enable Data Off Time           |     | 60     |     | 75     | ns    |       |  |

| <sup>t</sup> AH  | Address Hold Time Referenced to CE  | 60  |        | 75  |        | ns    |       |  |

| <sup>t</sup> AS  | Address Setup Time Referenced to CE | 0   |        | 0   |        | ns    |       |  |

| tP               | CE Precharge Time                   | 125 |        | 150 |        | ns    |       |  |

| <sup>t</sup> OEA | Output Enable Access Time           |     | 80     |     | 100    | ns    |       |  |

| tOEZ             | Output Enable Data Off Time         |     | 60     |     | 75     | ns    |       |  |

#### CAPACITANCE

$(0^{\circ}C \le T_{A} \le 70^{\circ}C)$

| SYM            | PARAMETER          | ТҮР | МАХ | UNITS | NOTES |

|----------------|--------------------|-----|-----|-------|-------|

| CI             | Input Capacitance  | 5   | 8   | pF    | 5     |

| с <sub>о</sub> | Output Capacitance | 7   | 15  | pF    | 5     |

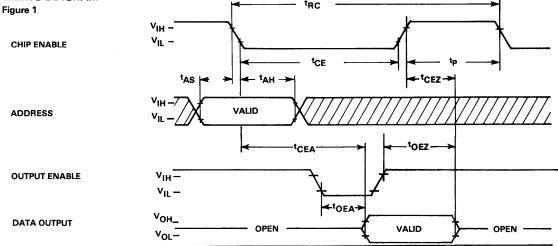

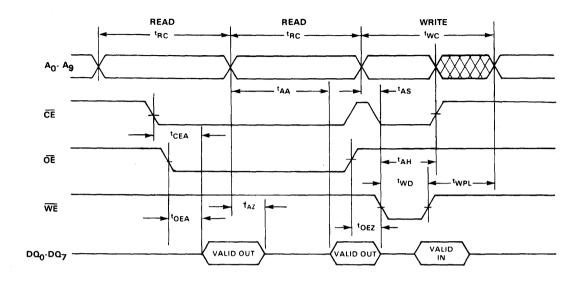

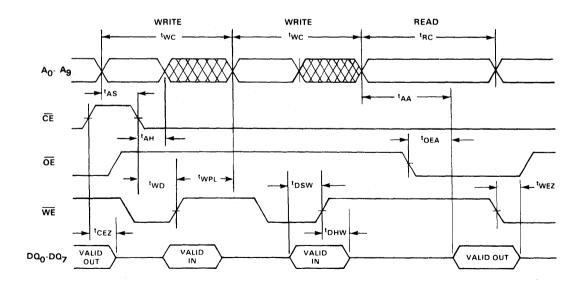

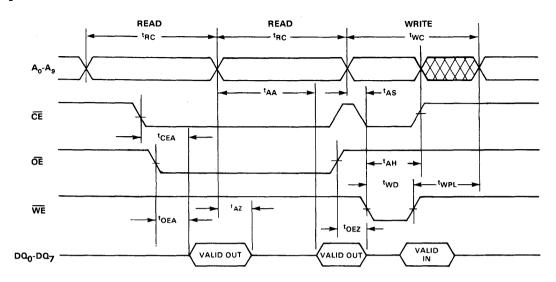

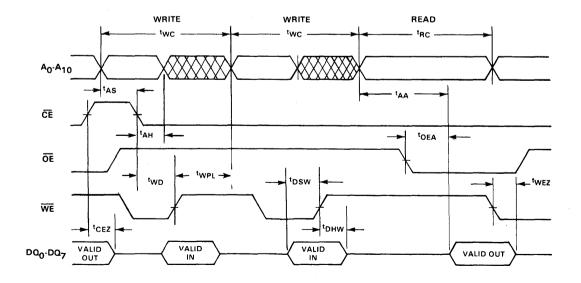

## **TIMING DIAGRAM**

#### NOTES:

- 1. Current is proportional to cycle rate.  $I_{\mbox{\scriptsize CC1}}$  is measured at the specified minimum cycle time. Data Outputs open.

- 2  $V_{IN} \approx 0V \text{ to } 5.5V$

- Device unselected; VOUT = OV to 5.5V 3.

- Measured with 2 TTL loads and 100pF, transition times = 20ns 4

- Capacitance measured with Boonton Meter or effective capacitance 5. calculated from the equation:

- $C = \Delta Q$  with  $\Delta V = 3$  volts

ΔV

#### **DESCRIPTION** (Continued)

28 pin DIP. This function matches that found on all of the new BYTEWYDE family of memories available from Mostek.

The use of clocked CE mode of operation provides an automatic power down mode of operation. The MK37000 features on chip address latches controlled by the CE input. Once address hold time is met, new address data can be provided to the device in anticipation of a subsequent cycle. It is not necessary to maintain the address up to access time to access valid data. The output enable function controls only the outputs and is not latched by CE. The CE input can be used for device selection and the OE input used to avoid bus conflicts so that outputs can be 'OR'ed together when using multiple devices.

Other system oriented features include fully TTL compatible inputs and outputs. The three state outputs, controlled by the  $\overline{OE}$  input, will drive a minimum of 2 standard TTL loads. The MK37000 operates from a single +5 volt power supply with a wide  $\pm$  10% 6. A minimum 2ms time delay is required after the application of V<sub>CC</sub> (+5) before proper device operation is achieved. CE must be at VIH for this time period.

7 CE high

tolerance, providing the widest operating margins available. The MK37000 is packaged in the industry standard 28 pin DIP. Pin 1 and 26 are not connected to allow easy upward compatibility with next generation higher density ROM which will use these pins for addresses. Pin 27 is not connected in order to maintain compatibility with RAMs which use this pin as a write enable (WE) control function.

Any application requiring a high performance, high bit density ROM can be satisfied by the MK37000. This device is ideally suited for 8 bit microprocessor systems such as those which utilize the MK3880. It can offer significant cost advantages over PROM.

#### **OPERATION**

The MK37000 is controlled by the chip enable (CE) and output enable (OE) inputs. A negative going edge at the CE input will activate the device and latch the addresses into the on chip address registers. The output buffers, under the control of  $\overline{OE}$ , will become active in  $\overline{CE}$  access

time (t<sub>CEA</sub>) if the output enable access time (t<sub>OEA</sub>) requirement is met. The on chip address register allows addresses to be changed after the specified hold time (t<sub>AH</sub>) in preparation for the next cycle. The outputs will remain valid and active until either  $\overrightarrow{CE}$  or  $\overrightarrow{OE}$  is returned to the inactive state. After chip deselect time (t<sub>CEZ</sub>) the output buffers will go to a high impedance state. The  $\overrightarrow{CE}$  input must remain inactive (high) between subsequent cycles for time tp to allow for precharging the nodes of the internal circuitry.

#### MK37000 ROM CODE DATA INPUT PROCEDURE

The preferred method of supplying code data to Mostek is in the form of programmed EPROMs (see table). In addition to the programmed set, Mostek requires an additional set of blank EPROMs for supplying customer code verification. When multiple EPROMs are required to describe the ROM they shall be designated in ascending address space with the numbers 1, 2, 3, etc. As an example, EPROM #1 would start with address space 0000 and go to 07FF for a 2K x 8 device. EPROM #2 would then start at address space 0800 and so on. A total of (4) 2K x 8 devices would be required to totally describe the address space of the 8K x 8 MK37000.

A paper printout and verification approval letter will accompany each verification EPROM set returned to the customer. Approval is considered to be excepted when the signed verification letter is returned to Mostek. The original set of EPROMs will be retained by Mostek for the duration of the prototyping process.

Acceptable EPROMs for Code Data

| EPROM     | # REQUIRED |

|-----------|------------|

| 2716/2516 | 4          |

| 2732      | 2          |

| 2764      | 1          |

## 256K-BIT MOS READ-ONLY MEMORY MK38000(P/N)-25

#### FEATURES

- □ Organized 32K x 8

- □ Pin compatible with Mostek's BYTEWYDE<sup>™</sup> Memory Family

- Access Time equals Cycle Time

- Static Operation

- Automatic Power Down

- □ CE and OE functions facilitate bus control

- Pin 27, logical don't care (X), permits interchange with BYTEWYDE<sup>TM</sup> RAM (WE)

- High performance

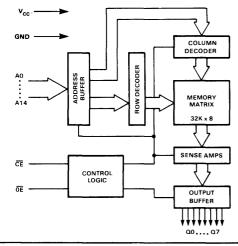

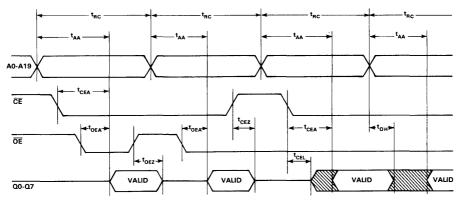

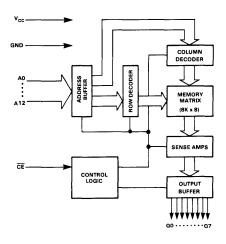

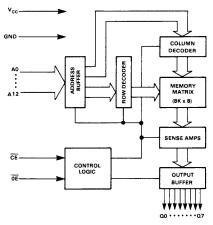

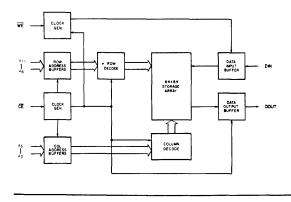

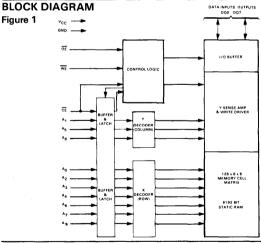

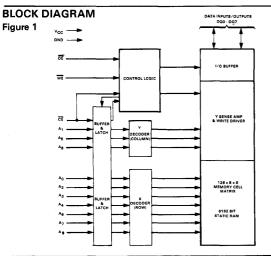

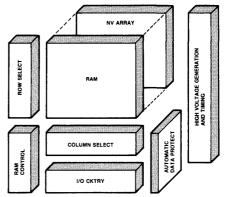

#### FUNCTIONAL DIAGRAM (MK38000) Figure 1

#### DESCRIPTION

The MK38000 is a N-channel, silicon gate MOS Read Only Memory, organized as 32,768 words by 8 bits. As a state-ofthe-art device, the MK38000 incorporates advanced circuit techniques designed to provide maximum circuit density and reliability with the highest possible performance, while maintaining low power dissipation and wide operating margins.

| Part No.   | Access Time | Cycle Time |

|------------|-------------|------------|

| MK38000-25 | 250 ns      | 250 ns     |

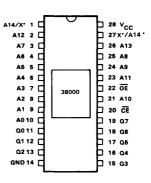

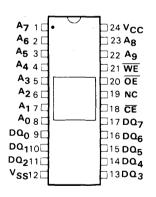

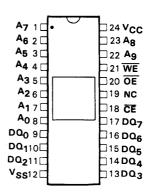

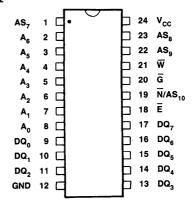

#### **PIN CONNECTIONS**

Figure 2

#### **PIN NAMES**

| A0-A14 | Address            | ŌĒ              | Output Enable |

|--------|--------------------|-----------------|---------------|

| CE     | Chip Enable        | V <sub>cc</sub> | +5 V          |

| Х      | Logical Don't Care | GND             | Ground        |

|        |                    | Q0-Q7           | Data Outputs  |

\*Alternate pinout see Note 11. Must be defined with ROM code.

#### TRUTH TABLE

| CE | ŌĒ | MODE     | OUTPUTS          | POWER   |

|----|----|----------|------------------|---------|

| н  | X  | Deselect | High-Z           | Standby |

| L  | н  | Inhibit  | High-Z           | Active  |

| L  | L  | Read     | D <sub>OUT</sub> | Active  |

As a member of the Mostek BYTEWYDE Memory Family, the MK38000 allows compatibility between RAM, ROM, and EPROM. The MK38000 can be used as a pin/function density upgrade to the MK37000 8K x 8 bit ROM.

The output enable function controls only the outputs. The  $\overline{CE}$  input can be used for device selection, and the  $\overline{OE}$  input can be used to avoid bus conflicts so that outputs can be 'OR'ed together when using a multiplexed or bi-directional bus.

Other system-oriented features include fully TTL compatible inputs and outputs. The MK38000 operates from a single +5 volt power supply. It is packaged in the industry standard 28-pin Dual In-line Package. Pin 27 may be a logical don't care in order to maintain compatibility with RAMs that use this pin as a write enable (WE) control function. Any application requiring a high performance, high bit density ROM can be satisfied by the MK38000. This device is ideally suited for 8-bit microprocessor systems, such as those utilizing the MK3880. It can offer significant cost advantages over PROM.

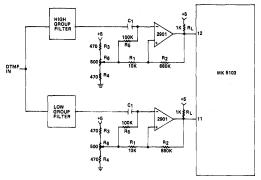

#### ABSOLUTE MAXIMUM RATINGS\*